spintronics

-

Success in Real-Time Observation of the Formation Process of Topological Solitons, a Core Technology for Next-Generation Information Transfer

< From left) Geonhyeong Park (Ph.D. Candidate), Yun-Seok Choi (Ph.D.), Professor Dong Ki Yoon, and Changjae Lee (Ph.D. Candidate) of the Department of Chemistry >

Professor Dong Ki Yoon's research team in the Department of Chemistry at KAIST announced on the 11th that they have succeeded in controlling the formation of topological solitons in a regular, large-area manner through the self-assembly of chiral liquid crystal materials and observing their formation process in real-time.

A soliton refers to a phenomenon where a specific wave persists without dissipating through interaction with its surroundings. In particular, even when a wave is transmitted over long distances, it retains its unique information until it reaches the desired destination. Therefore, in today's digital society, which is susceptible to hacking, solitons are highly anticipated to be the core of future communication due to their inherent high stability. Furthermore, topological solitons created using organic liquid crystal molecules are expected to be utilized as next-generation anti-counterfeiting devices and memory elements due to their unique spin directionality.

Professor Yoon's team specifically revealed the formation process of topological solitons in this study, which had not been observable in real-time under mild conditions such as room temperature until now. This was made possible by using self-assembling chiral liquid crystal materials in a confined space created by air pillars.

This research, in which Geonhyeong Park (Ph.D. Candidate, Department of Chemistry) and Dr. Ahram Suh participated as co-first authors, and Dr. Yun-Seok Choi and Changjae Lee (Ph.D. Candidate) from the same group also participated, was published online in the international journal 'Advanced Materials' on June 5th and is scheduled to be featured as the back cover of the July issue. (Paper title: "Fabrication of Arrays of Topological Solitons in Patterned Chiral Liquid Crystals for Real-Time Observation of Morphogenesis")

< Figure 1. Schematic diagram of the research>

< Figure 2. Real-time observation of topological soliton formation using liquid crystals>

In this study, Professor Yoon's team implemented topological soliton structures at approximately 30 degrees Celsius, similar to room temperature, using chiral (asymmetric) liquid crystal materials instead of the conventional liquid crystal molecules widely used as core materials in liquid crystal displays (LCDs). Generally, complex equipment is required to control the formation of topological solitons, and their formation time is very short, which has hindered research into their formation process until now.

To achieve regular formation and control of topological solitons formed by chiral liquid crystal molecules, Professor Yoon's team precisely controlled a combination of vertical alignment layers, which can orient molecules vertically, and air pillars. Specifically, they prepared concave patterns based on circular silicon material, several micrometers (one-millionth of a meter) in size, coated with a vertical alignment layer, and a glass substrate. By adjusting the gap to several micrometers and injecting chiral liquid crystal material, air pillars were spontaneously formed on the concave patterns. Subsequently, the liquid crystal molecules were vertically aligned on all substrates, inevitably causing regular distortions between the substrates, and between the substrate and the air pillars, thus developing a system where chiral molecular structures, i.e., topological solitons, could be formed.

The key to the formation and control of topological solitons lies in controlling the thermal phase transition to occur regularly as desired when cooling from the isotropic phase temperature (approximately 40 degrees Celsius) to the liquid crystal phase temperature (approximately 30 degrees Celsius), where the liquid crystal material near the air pillars is cooler than the liquid crystal material between the glass substrate and the silicon patterned parts. This is consistent with the everyday wisdom of eating steamed eggs from a 'Ttukbaegi' (earthen pot) by starting from the relatively cooler part exposed to the air (near the air pillars) rather than the hot pot part (silicon or glass substrate part).

Through real-time analysis, the research team elucidated that topological defects are formed by the naturally formed air pillars through controlled thermal phase transition, and topological solitons are formed only at the locations of these defects. This analysis technique has the potential for application in various fields, including the interpretation of topological soliton formation found in other physical phenomena such as skyrmion particles in electromagnetism.

< Figure 3. Snapshots during the formation process of regularly arranged topological solitons>

Professor Dong Ki Yoon stated, "General topological solitons are known to be highly stable, capable only of generation or annihilation. Through the results of this research, we can understand the formation process of solitons in more detail, and they can be used as spintronics application technology, considered a next-generation semiconductor device for storing and recording information."

This research was conducted in collaboration with Professor Ivan Smalyukh's laboratory at the University of Colorado, Department of Physics, and was supported by the Multiscale Chiral Structures Research Center and strategic projects of the National Research Foundation of Korea under the Ministry of Science and ICT.

2022.07.11 View 623

Success in Real-Time Observation of the Formation Process of Topological Solitons, a Core Technology for Next-Generation Information Transfer

< From left) Geonhyeong Park (Ph.D. Candidate), Yun-Seok Choi (Ph.D.), Professor Dong Ki Yoon, and Changjae Lee (Ph.D. Candidate) of the Department of Chemistry >

Professor Dong Ki Yoon's research team in the Department of Chemistry at KAIST announced on the 11th that they have succeeded in controlling the formation of topological solitons in a regular, large-area manner through the self-assembly of chiral liquid crystal materials and observing their formation process in real-time.

A soliton refers to a phenomenon where a specific wave persists without dissipating through interaction with its surroundings. In particular, even when a wave is transmitted over long distances, it retains its unique information until it reaches the desired destination. Therefore, in today's digital society, which is susceptible to hacking, solitons are highly anticipated to be the core of future communication due to their inherent high stability. Furthermore, topological solitons created using organic liquid crystal molecules are expected to be utilized as next-generation anti-counterfeiting devices and memory elements due to their unique spin directionality.

Professor Yoon's team specifically revealed the formation process of topological solitons in this study, which had not been observable in real-time under mild conditions such as room temperature until now. This was made possible by using self-assembling chiral liquid crystal materials in a confined space created by air pillars.

This research, in which Geonhyeong Park (Ph.D. Candidate, Department of Chemistry) and Dr. Ahram Suh participated as co-first authors, and Dr. Yun-Seok Choi and Changjae Lee (Ph.D. Candidate) from the same group also participated, was published online in the international journal 'Advanced Materials' on June 5th and is scheduled to be featured as the back cover of the July issue. (Paper title: "Fabrication of Arrays of Topological Solitons in Patterned Chiral Liquid Crystals for Real-Time Observation of Morphogenesis")

< Figure 1. Schematic diagram of the research>

< Figure 2. Real-time observation of topological soliton formation using liquid crystals>

In this study, Professor Yoon's team implemented topological soliton structures at approximately 30 degrees Celsius, similar to room temperature, using chiral (asymmetric) liquid crystal materials instead of the conventional liquid crystal molecules widely used as core materials in liquid crystal displays (LCDs). Generally, complex equipment is required to control the formation of topological solitons, and their formation time is very short, which has hindered research into their formation process until now.

To achieve regular formation and control of topological solitons formed by chiral liquid crystal molecules, Professor Yoon's team precisely controlled a combination of vertical alignment layers, which can orient molecules vertically, and air pillars. Specifically, they prepared concave patterns based on circular silicon material, several micrometers (one-millionth of a meter) in size, coated with a vertical alignment layer, and a glass substrate. By adjusting the gap to several micrometers and injecting chiral liquid crystal material, air pillars were spontaneously formed on the concave patterns. Subsequently, the liquid crystal molecules were vertically aligned on all substrates, inevitably causing regular distortions between the substrates, and between the substrate and the air pillars, thus developing a system where chiral molecular structures, i.e., topological solitons, could be formed.

The key to the formation and control of topological solitons lies in controlling the thermal phase transition to occur regularly as desired when cooling from the isotropic phase temperature (approximately 40 degrees Celsius) to the liquid crystal phase temperature (approximately 30 degrees Celsius), where the liquid crystal material near the air pillars is cooler than the liquid crystal material between the glass substrate and the silicon patterned parts. This is consistent with the everyday wisdom of eating steamed eggs from a 'Ttukbaegi' (earthen pot) by starting from the relatively cooler part exposed to the air (near the air pillars) rather than the hot pot part (silicon or glass substrate part).

Through real-time analysis, the research team elucidated that topological defects are formed by the naturally formed air pillars through controlled thermal phase transition, and topological solitons are formed only at the locations of these defects. This analysis technique has the potential for application in various fields, including the interpretation of topological soliton formation found in other physical phenomena such as skyrmion particles in electromagnetism.

< Figure 3. Snapshots during the formation process of regularly arranged topological solitons>

Professor Dong Ki Yoon stated, "General topological solitons are known to be highly stable, capable only of generation or annihilation. Through the results of this research, we can understand the formation process of solitons in more detail, and they can be used as spintronics application technology, considered a next-generation semiconductor device for storing and recording information."

This research was conducted in collaboration with Professor Ivan Smalyukh's laboratory at the University of Colorado, Department of Physics, and was supported by the Multiscale Chiral Structures Research Center and strategic projects of the National Research Foundation of Korea under the Ministry of Science and ICT.

2022.07.11 View 623 -

Highly Efficient Charge-to-Spin Interconversion in Graphene Heterostructures

Researchers present a new route for designing a graphene-based active spintronic component

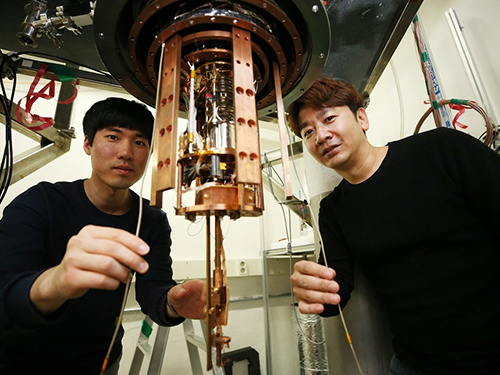

KAIST physicists described a route to design the energy-efficient generation, manipulation and detection of spin currents using nonmagnetic two-dimensional materials. The research team, led by Professor Sungjae Cho, observed highly efficient charge-to-spin interconversion via the gate-tunable Rashba-Edelstien effect (REE) in graphene heterostructures.

This research paves the way for the application of graphene as an active spintronic component for generating, controlling, and detecting spin current without ferromagnetic electrodes or magnetic fields.

Graphene is a promising spintronic component owing to its long spin diffusion length. However, its small spin-orbit coupling limits the potential of graphene in spintronic applications since graphene cannot be used to generate, control, or detect spin current.

“We successfully increased the spin-orbit coupling of graphene by stacking graphene on top of 2H-TaS2, which is one of the transition metal dichalcogenide materials with the largest spin-orbit coupling. Graphene now can be used to generate, control, and detect spin current,” Professor Cho said.

The Rashba-Edelstein effect is a physical mechanism that enables charge current-to-spin current interconversion by spin-dependent band structure induced by the Rashba effect, a momentum-dependent splitting of spin bands in low-dimensional condensed matter systems.

Professor Cho’s group demonstrated the gate-tunable Rashba-Edelstein effect in a multilayer graphene for the first time. The Rahsba-Edelstein effect allows the two-dimensional conduction electrons of graphene to be magnetized by an applied charge current and form a spin current. Furthermore, as the Fermi level of graphene, tuned by gate voltage, moves from the valence to conduction band, the spin current generated by graphene reversed its spin direction.

This spin reversal is useful in the design of low-power-consumption transistors utilizing spins in that it provides the carrier “On” state with spin up holes (or spin down electrons) and the "Off" state with zero net spin polarization at so called “charge neutrality point” where numbers of electrons and holes are equal.

“Our work is the first demonstration of charge-to-spin interconversion in a metallic TMD (transition-metal dichalcogenides) and graphene heterostructure with a spin polarization state controlled by a gate. We expect that the all-electrical spin-switching effect and the reversal of non-equilibrium spin polarization by the application of gate voltage is applicable for the energy-efficient generation and manipulation of spin currents using nonmagnetic van der Waals materials,” explained Professor Cho.

This study (https://pubs.acs.org/doi/10.1021/acsnano.0c01037) was supported by the National Research Foundation of Korea.

Publication:

Lijun Li, Jin Zhang, Gyuho Myeong, Wongil Shin, Hongsik Lim, Boram Kim, Seungho Kim, Taehyeok Jin, Stuart Cavill, Beom Seo Kim, Changyoung Kim, Johannes Lischner, Aires Ferreira, and Sungjae Cho, Gate-Tunable Reversible Rashba−Edelstein Effect in a Few-Layer Graphene/2H-TaS2 Heterostructure at Room Temperature. ACS Nano 2020. Link to download the paper: https://pubs.acs.org/doi/10.1021/acsnano.0c01037

Profile:

Professor Sungjae Cho, PhD

sungjae.cho@kaist.ac.kr

http://qtak.kaist.ac.kr

Department of Physics

Korea Advanced Institute of Science and Technology (KAIST)

https://www.kaist.ac.kr

Daejeon 34141, Korea

2020.05.18 View 11268

Highly Efficient Charge-to-Spin Interconversion in Graphene Heterostructures

Researchers present a new route for designing a graphene-based active spintronic component

KAIST physicists described a route to design the energy-efficient generation, manipulation and detection of spin currents using nonmagnetic two-dimensional materials. The research team, led by Professor Sungjae Cho, observed highly efficient charge-to-spin interconversion via the gate-tunable Rashba-Edelstien effect (REE) in graphene heterostructures.

This research paves the way for the application of graphene as an active spintronic component for generating, controlling, and detecting spin current without ferromagnetic electrodes or magnetic fields.

Graphene is a promising spintronic component owing to its long spin diffusion length. However, its small spin-orbit coupling limits the potential of graphene in spintronic applications since graphene cannot be used to generate, control, or detect spin current.

“We successfully increased the spin-orbit coupling of graphene by stacking graphene on top of 2H-TaS2, which is one of the transition metal dichalcogenide materials with the largest spin-orbit coupling. Graphene now can be used to generate, control, and detect spin current,” Professor Cho said.

The Rashba-Edelstein effect is a physical mechanism that enables charge current-to-spin current interconversion by spin-dependent band structure induced by the Rashba effect, a momentum-dependent splitting of spin bands in low-dimensional condensed matter systems.

Professor Cho’s group demonstrated the gate-tunable Rashba-Edelstein effect in a multilayer graphene for the first time. The Rahsba-Edelstein effect allows the two-dimensional conduction electrons of graphene to be magnetized by an applied charge current and form a spin current. Furthermore, as the Fermi level of graphene, tuned by gate voltage, moves from the valence to conduction band, the spin current generated by graphene reversed its spin direction.

This spin reversal is useful in the design of low-power-consumption transistors utilizing spins in that it provides the carrier “On” state with spin up holes (or spin down electrons) and the "Off" state with zero net spin polarization at so called “charge neutrality point” where numbers of electrons and holes are equal.

“Our work is the first demonstration of charge-to-spin interconversion in a metallic TMD (transition-metal dichalcogenides) and graphene heterostructure with a spin polarization state controlled by a gate. We expect that the all-electrical spin-switching effect and the reversal of non-equilibrium spin polarization by the application of gate voltage is applicable for the energy-efficient generation and manipulation of spin currents using nonmagnetic van der Waals materials,” explained Professor Cho.

This study (https://pubs.acs.org/doi/10.1021/acsnano.0c01037) was supported by the National Research Foundation of Korea.

Publication:

Lijun Li, Jin Zhang, Gyuho Myeong, Wongil Shin, Hongsik Lim, Boram Kim, Seungho Kim, Taehyeok Jin, Stuart Cavill, Beom Seo Kim, Changyoung Kim, Johannes Lischner, Aires Ferreira, and Sungjae Cho, Gate-Tunable Reversible Rashba−Edelstein Effect in a Few-Layer Graphene/2H-TaS2 Heterostructure at Room Temperature. ACS Nano 2020. Link to download the paper: https://pubs.acs.org/doi/10.1021/acsnano.0c01037

Profile:

Professor Sungjae Cho, PhD

sungjae.cho@kaist.ac.kr

http://qtak.kaist.ac.kr

Department of Physics

Korea Advanced Institute of Science and Technology (KAIST)

https://www.kaist.ac.kr

Daejeon 34141, Korea

2020.05.18 View 11268 -

Black Phosphorous Tunnel Field-Effect Transistor as an Alternative Ultra-low Power Switch

Researchers have reported a black phosphorus transistor that can be used as an alternative ultra-low power switch. A research team led by Professor Sungjae Cho in the KAIST Department of Physics developed a thickness-controlled black phosphorous tunnel field-effect transistor (TFET) that shows 10-times lower switching power consumption as well as 10,000-times lower standby power consumption than conventional complementary metal-oxide-semiconductor (CMOS) transistors.

The research team said they developed fast and low-power transistors that can replace conventional CMOS transistors. In particular, they solved problems that have degraded TFET operation speed and performance, paving the way to extend Moore’s Law.

In the study featured in Nature Nanotechnology last month, Professor Cho’s team reported a natural heterojunction TFET with spatially varying layer thickness in black phosphorous without interface problems. They achieved record-low average subthreshold swing values over 4-5 dec of current and record-high, on-state current, which allows the TFETs to operate as fast as conventional CMOS transistors with as much lower power consumption.

"We successfully developed the first transistor that achieved the essential criteria for fast, low-power switching. Our newly developed TFETs can replace CMOS transistors by solving a major issue regarding the performance degradation of TFETs,"Professor Cho said.

The continuous down-scaling of transistors has been the key to the successful development of current information technology. However, with Moore’s Law reaching its limits due to the increased power consumption, the development of new alternative transistor designs has emerged as an urgent need.

Reducing both switching and standby power consumption while further scaling transistors requires overcoming the thermionic limit of subthreshold swing, which is defined as the required voltage per ten-fold current increase in the subthreshold region. In order to reduce both the switching and standby power of CMOS circuits, it is critical to reduce the subthreshold swing of the transistors.

However, there is fundamental subthreshold swing limit of 60 mV/dec in CMOS transistors, which originates from thermal carrier injection. The International Roadmap for Devices and Systems has already predicted that new device geometries with new materials beyond CMOS will be required to address transistor scaling challenges in the near future. In particular, TFETs have been suggested as a major alternative to CMOS transistors, since the subthreshold swing in TFETs can be substantially reduced below the thermionic limit of 60 mV/dec. TFETs operate via quantum tunneling, which does not limit subthreshold swing as in thermal injection of CMOS transistors.

In particular, heterojunction TFETs hold significant promise for delivering both low subthreshold swing and high on-state current. High on-current is essential for the fast operation of transistors since charging a device to on state takes a longer time with lower currents. Unlike theoretical expectations, previously developed heterojunction TFETs show 100-100,000x lower on-state current (100-100,000x slower operation speeds) than CMOS transistors due to interface problems in the heterojunction. This low operation speed impedes the replacement of CMOS transistors with low-power TFETs.

Professor Cho said, “We have demonstrated for the first time, to the best of our knowledge, TFET optimization for both fast and ultra-low-power operations, which is essential to replace CMOS transistors for low-power applications.” He said he is very delighted to extend Moore’s Law, which may eventually affect almost every aspect of life and society. This study (https://doi.org/10.1038/s41565-019-0623-7) was supported by the National Research Foundation of Korea.

Publication:

Kim et al. (2020) Thickness-controlled black phosphorus tunnel field-effect transistor for low-power switches. Nature Nanotechnology. Available online at https://doi.org/10.1038/s41565-019-0623-7

Profile:

Professor Sungjae Cho

sungjae.cho@kaist.ac.kr

Department of Physics

http://qtak.kaist.ac.kr/

KAIST

Profile:

Seungho Kim, PhD Candidate

krksh21@kaist.ac.kr

Department of Physics

http://qtak.kaist.ac.kr/

KAIST

(END)

2020.02.21 View 13623

Black Phosphorous Tunnel Field-Effect Transistor as an Alternative Ultra-low Power Switch

Researchers have reported a black phosphorus transistor that can be used as an alternative ultra-low power switch. A research team led by Professor Sungjae Cho in the KAIST Department of Physics developed a thickness-controlled black phosphorous tunnel field-effect transistor (TFET) that shows 10-times lower switching power consumption as well as 10,000-times lower standby power consumption than conventional complementary metal-oxide-semiconductor (CMOS) transistors.

The research team said they developed fast and low-power transistors that can replace conventional CMOS transistors. In particular, they solved problems that have degraded TFET operation speed and performance, paving the way to extend Moore’s Law.

In the study featured in Nature Nanotechnology last month, Professor Cho’s team reported a natural heterojunction TFET with spatially varying layer thickness in black phosphorous without interface problems. They achieved record-low average subthreshold swing values over 4-5 dec of current and record-high, on-state current, which allows the TFETs to operate as fast as conventional CMOS transistors with as much lower power consumption.

"We successfully developed the first transistor that achieved the essential criteria for fast, low-power switching. Our newly developed TFETs can replace CMOS transistors by solving a major issue regarding the performance degradation of TFETs,"Professor Cho said.

The continuous down-scaling of transistors has been the key to the successful development of current information technology. However, with Moore’s Law reaching its limits due to the increased power consumption, the development of new alternative transistor designs has emerged as an urgent need.

Reducing both switching and standby power consumption while further scaling transistors requires overcoming the thermionic limit of subthreshold swing, which is defined as the required voltage per ten-fold current increase in the subthreshold region. In order to reduce both the switching and standby power of CMOS circuits, it is critical to reduce the subthreshold swing of the transistors.

However, there is fundamental subthreshold swing limit of 60 mV/dec in CMOS transistors, which originates from thermal carrier injection. The International Roadmap for Devices and Systems has already predicted that new device geometries with new materials beyond CMOS will be required to address transistor scaling challenges in the near future. In particular, TFETs have been suggested as a major alternative to CMOS transistors, since the subthreshold swing in TFETs can be substantially reduced below the thermionic limit of 60 mV/dec. TFETs operate via quantum tunneling, which does not limit subthreshold swing as in thermal injection of CMOS transistors.

In particular, heterojunction TFETs hold significant promise for delivering both low subthreshold swing and high on-state current. High on-current is essential for the fast operation of transistors since charging a device to on state takes a longer time with lower currents. Unlike theoretical expectations, previously developed heterojunction TFETs show 100-100,000x lower on-state current (100-100,000x slower operation speeds) than CMOS transistors due to interface problems in the heterojunction. This low operation speed impedes the replacement of CMOS transistors with low-power TFETs.

Professor Cho said, “We have demonstrated for the first time, to the best of our knowledge, TFET optimization for both fast and ultra-low-power operations, which is essential to replace CMOS transistors for low-power applications.” He said he is very delighted to extend Moore’s Law, which may eventually affect almost every aspect of life and society. This study (https://doi.org/10.1038/s41565-019-0623-7) was supported by the National Research Foundation of Korea.

Publication:

Kim et al. (2020) Thickness-controlled black phosphorus tunnel field-effect transistor for low-power switches. Nature Nanotechnology. Available online at https://doi.org/10.1038/s41565-019-0623-7

Profile:

Professor Sungjae Cho

sungjae.cho@kaist.ac.kr

Department of Physics

http://qtak.kaist.ac.kr/

KAIST

Profile:

Seungho Kim, PhD Candidate

krksh21@kaist.ac.kr

Department of Physics

http://qtak.kaist.ac.kr/

KAIST

(END)

2020.02.21 View 13623 -

Professor Byong-Guk Park Named Scientist of October

< Professor Byong-Guk Park >

Professor Byong-Guk Park from the Department of Materials Science and Engineering was selected as the ‘Scientist of the Month’ for October 2019 by the Ministry of Science and ICT and the National Research Foundation of Korea. Professor Park was recognized for his contributions to the advancement of spin-orbit torque (SOT)-based magnetic random access memory (MRAM) technology. He received 10 million KRW in prize money.

A next-generation, non-volatile memory device MRAM consists of thin magnetic films. It can be applied in “logic-in-memory” devices, in which logic and memory functionalities coexist, thus drastically improving the performance of complementary metal-oxide semiconductor (CMOS) processors. Conventional MRAM technology is limited in its ability to increase the operation speed of a memory device while maintaining a high density.

Professor Park tackled this challenge by introducing a new material, antiferromagnet (IrMn), that generates a sizable amount of SOT as well as an exchange-bias field, which makes successful data writing possible without an external magnetic field. This research outcome paved the way for the development of MRAM, which has a simple device structure but features high speeds and density.

Professor Park said, “I feel rewarded to have forwarded the feasibility and applicability of MRAM. I will continue devoting myself to studying further on the development of new materials that can help enhance the performance of memory devices."

(END)

2019.10.10 View 11704

Professor Byong-Guk Park Named Scientist of October

< Professor Byong-Guk Park >

Professor Byong-Guk Park from the Department of Materials Science and Engineering was selected as the ‘Scientist of the Month’ for October 2019 by the Ministry of Science and ICT and the National Research Foundation of Korea. Professor Park was recognized for his contributions to the advancement of spin-orbit torque (SOT)-based magnetic random access memory (MRAM) technology. He received 10 million KRW in prize money.

A next-generation, non-volatile memory device MRAM consists of thin magnetic films. It can be applied in “logic-in-memory” devices, in which logic and memory functionalities coexist, thus drastically improving the performance of complementary metal-oxide semiconductor (CMOS) processors. Conventional MRAM technology is limited in its ability to increase the operation speed of a memory device while maintaining a high density.

Professor Park tackled this challenge by introducing a new material, antiferromagnet (IrMn), that generates a sizable amount of SOT as well as an exchange-bias field, which makes successful data writing possible without an external magnetic field. This research outcome paved the way for the development of MRAM, which has a simple device structure but features high speeds and density.

Professor Park said, “I feel rewarded to have forwarded the feasibility and applicability of MRAM. I will continue devoting myself to studying further on the development of new materials that can help enhance the performance of memory devices."

(END)

2019.10.10 View 11704