Nano-Oriented+Bio-Electronics+Lab

-

The World’s First Hacking-preventing Cryptographic Semiconductor Chip

With the dramatic increase in the amount of information exchanged between components or devices in the 5G/6G era, such as for the Internet of Things (IoT) and autonomous driving, hacking attacks are becoming more sophisticated. Consequently, enhancing security functions is essential for safely transmitting data between and among devices.

On February 29th, a KAIST research team led by Professors Yang-gyu Choi and Seung-tak Ryu from the School of Electrical Engineering announced the successful development of the world's first security cryptographic semiconductor.

The team has developed the Cryptoristor, a cryptographic transistor based on FinFET technology, produced through a 100% silicon-compatible process, for the first time in the world. Cryptoristor is a random number generator (RNG) with unparalleled characteristics, featuring a unique structure comprising a single transistor and a distinctive mechanism.

In all security environments, including artificial intelligence, the most crucial element is the RNG. In the most commonly used security chip, the Advanced Encryption Standard (AES), the RNG is a core component, occupying approximately 75% of the total chip area and more than 85% of its energy consumption. Hence, there is an urgent need for the development of low-power/ultra-small RNGs suitable for mobile or IoT devices.

Existing RNGs come with limitations as they lack compatibility with silicon CMOS processes and circuit-based RNGs occupy a large surface area.

In contrast, the team’s newly developed Cryptoristor, a cryptographic semiconductor based on a single-component structure, consumes and occupies less than .001 of the power and area compared to the current chips being used. Utilizing the inherent randomness of FinFETs, fabricated on a Silicon-on-Insulator (SOI) substrate with an insulating layer formed beneath the silicon, the team developed an RNG that unpredictably produces zeroes and ones.

< Figure 1. Conceptual diagram of the security cryptographic transistor device. >

Generally speaking, preventing hackers from predicting the encrypted algorithms during data exchanges through mobile devices is pivotal. Therefore, this method ensures unpredictability by generating random sequences of zeroes and ones that change every time.

Moreover, while the Cryptoristor-based RNG research is the world's first of its kind without any international implementation cases, it shares the same transistor structure as existing logic or memory components. This enables 100% production through rapid mass production processes using existing semiconductor facilities at a low cost.

Seung-il Kim, a PhD student who led the research, explained the significance of the study, stating, "As a cryptographic semiconductor, the ultra-small/low-power random number generator enhances security through its distinctive unpredictability, supporting safe hyperconnectivity with secure transmissions between chips or devices. Particularly, compared to previous research, it offers excellent advantages in terms of energy consumption, integration density, and cost, making it suitable for IoT device environments."

This research, with master’s student Hyung-jin Yoo as the co-author, was officially published in the online edition of Science Advances, a sister journal of Science, in February 2024 (research paper title: Cryptographic transistor for true random number generator with low power consumption).

This research received support from the Next-Generation Intelligent Semiconductor Technology Development Project and the Core Technology Development Project for the National Semiconductor Research Laboratory.

2024.03.07 View 7572

The World’s First Hacking-preventing Cryptographic Semiconductor Chip

With the dramatic increase in the amount of information exchanged between components or devices in the 5G/6G era, such as for the Internet of Things (IoT) and autonomous driving, hacking attacks are becoming more sophisticated. Consequently, enhancing security functions is essential for safely transmitting data between and among devices.

On February 29th, a KAIST research team led by Professors Yang-gyu Choi and Seung-tak Ryu from the School of Electrical Engineering announced the successful development of the world's first security cryptographic semiconductor.

The team has developed the Cryptoristor, a cryptographic transistor based on FinFET technology, produced through a 100% silicon-compatible process, for the first time in the world. Cryptoristor is a random number generator (RNG) with unparalleled characteristics, featuring a unique structure comprising a single transistor and a distinctive mechanism.

In all security environments, including artificial intelligence, the most crucial element is the RNG. In the most commonly used security chip, the Advanced Encryption Standard (AES), the RNG is a core component, occupying approximately 75% of the total chip area and more than 85% of its energy consumption. Hence, there is an urgent need for the development of low-power/ultra-small RNGs suitable for mobile or IoT devices.

Existing RNGs come with limitations as they lack compatibility with silicon CMOS processes and circuit-based RNGs occupy a large surface area.

In contrast, the team’s newly developed Cryptoristor, a cryptographic semiconductor based on a single-component structure, consumes and occupies less than .001 of the power and area compared to the current chips being used. Utilizing the inherent randomness of FinFETs, fabricated on a Silicon-on-Insulator (SOI) substrate with an insulating layer formed beneath the silicon, the team developed an RNG that unpredictably produces zeroes and ones.

< Figure 1. Conceptual diagram of the security cryptographic transistor device. >

Generally speaking, preventing hackers from predicting the encrypted algorithms during data exchanges through mobile devices is pivotal. Therefore, this method ensures unpredictability by generating random sequences of zeroes and ones that change every time.

Moreover, while the Cryptoristor-based RNG research is the world's first of its kind without any international implementation cases, it shares the same transistor structure as existing logic or memory components. This enables 100% production through rapid mass production processes using existing semiconductor facilities at a low cost.

Seung-il Kim, a PhD student who led the research, explained the significance of the study, stating, "As a cryptographic semiconductor, the ultra-small/low-power random number generator enhances security through its distinctive unpredictability, supporting safe hyperconnectivity with secure transmissions between chips or devices. Particularly, compared to previous research, it offers excellent advantages in terms of energy consumption, integration density, and cost, making it suitable for IoT device environments."

This research, with master’s student Hyung-jin Yoo as the co-author, was officially published in the online edition of Science Advances, a sister journal of Science, in February 2024 (research paper title: Cryptographic transistor for true random number generator with low power consumption).

This research received support from the Next-Generation Intelligent Semiconductor Technology Development Project and the Core Technology Development Project for the National Semiconductor Research Laboratory.

2024.03.07 View 7572 -

Brain-Inspired Highly Scalable Neuromorphic Hardware Presented

Neurons and synapses based on single transistor can dramatically reduce the hardware cost and accelerate the commercialization of neuromorphic hardware

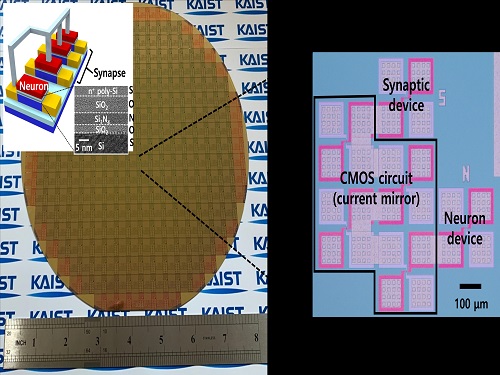

KAIST researchers fabricated a brain-inspired highly scalable neuromorphic hardware by co-integrating single transistor neurons and synapses. Using standard silicon complementary metal-oxide-semiconductor (CMOS) technology, the neuromorphic hardware is expected to reduce chip cost and simplify fabrication procedures.

The research team led by Yang-Kyu Choi and Sung-Yool Choi produced a neurons and synapses based on single transistor for highly scalable neuromorphic hardware and showed the ability to recognize text and face images. This research was featured in Science Advances on August 4.

Neuromorphic hardware has attracted a great deal of attention because of its artificial intelligence functions, but consuming ultra-low power of less than 20 watts by mimicking the human brain. To make neuromorphic hardware work, a neuron that generates a spike when integrating a certain signal, and a synapse remembering the connection between two neurons are necessary, just like the biological brain. However, since neurons and synapses constructed on digital or analog circuits occupy a large space, there is a limit in terms of hardware efficiency and costs. Since the human brain consists of about 1011 neurons and 1014 synapses, it is necessary to improve the hardware cost in order to apply it to mobile and IoT devices.

To solve the problem, the research team mimicked the behavior of biological neurons and synapses with a single transistor, and co-integrated them onto an 8-inch wafer. The manufactured neuromorphic transistors have the same structure as the transistors for memory and logic that are currently mass-produced. In addition, the neuromorphic transistors proved for the first time that they can be implemented with a ‘Janus structure’ that functions as both neuron and synapse, just like coins have heads and tails.

Professor Yang-Kyu Choi said that this work can dramatically reduce the hardware cost by replacing the neurons and synapses that were based on complex digital and analog circuits with a single transistor. "We have demonstrated that neurons and synapses can be implemented using a single transistor," said Joon-Kyu Han, the first author. "By co-integrating single transistor neurons and synapses on the same wafer using a standard CMOS process, the hardware cost of the neuromorphic hardware has been improved, which will accelerate the commercialization of neuromorphic hardware,” Han added.This research was supported by the National Research Foundation (NRF) and IC Design Education Center (IDEC).

-PublicationJoon-Kyu Han, Sung-Yool Choi, Yang-Kyu Choi, et al.“Cointegration of single-transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware,” Science Advances (DOI: 10.1126/sciadv.abg8836)

-ProfileProfessor Yang-Kyu ChoiNano-Oriented Bio-Electronics Labhttps://sites.google.com/view/nobelab/

School of Electrical EngineeringKAIST

Professor Sung-Yool ChoiMolecular and Nano Device Laboratoryhttps://www.mndl.kaist.ac.kr/

School of Electrical EngineeringKAIST

2021.08.05 View 11458

Brain-Inspired Highly Scalable Neuromorphic Hardware Presented

Neurons and synapses based on single transistor can dramatically reduce the hardware cost and accelerate the commercialization of neuromorphic hardware

KAIST researchers fabricated a brain-inspired highly scalable neuromorphic hardware by co-integrating single transistor neurons and synapses. Using standard silicon complementary metal-oxide-semiconductor (CMOS) technology, the neuromorphic hardware is expected to reduce chip cost and simplify fabrication procedures.

The research team led by Yang-Kyu Choi and Sung-Yool Choi produced a neurons and synapses based on single transistor for highly scalable neuromorphic hardware and showed the ability to recognize text and face images. This research was featured in Science Advances on August 4.

Neuromorphic hardware has attracted a great deal of attention because of its artificial intelligence functions, but consuming ultra-low power of less than 20 watts by mimicking the human brain. To make neuromorphic hardware work, a neuron that generates a spike when integrating a certain signal, and a synapse remembering the connection between two neurons are necessary, just like the biological brain. However, since neurons and synapses constructed on digital or analog circuits occupy a large space, there is a limit in terms of hardware efficiency and costs. Since the human brain consists of about 1011 neurons and 1014 synapses, it is necessary to improve the hardware cost in order to apply it to mobile and IoT devices.

To solve the problem, the research team mimicked the behavior of biological neurons and synapses with a single transistor, and co-integrated them onto an 8-inch wafer. The manufactured neuromorphic transistors have the same structure as the transistors for memory and logic that are currently mass-produced. In addition, the neuromorphic transistors proved for the first time that they can be implemented with a ‘Janus structure’ that functions as both neuron and synapse, just like coins have heads and tails.

Professor Yang-Kyu Choi said that this work can dramatically reduce the hardware cost by replacing the neurons and synapses that were based on complex digital and analog circuits with a single transistor. "We have demonstrated that neurons and synapses can be implemented using a single transistor," said Joon-Kyu Han, the first author. "By co-integrating single transistor neurons and synapses on the same wafer using a standard CMOS process, the hardware cost of the neuromorphic hardware has been improved, which will accelerate the commercialization of neuromorphic hardware,” Han added.This research was supported by the National Research Foundation (NRF) and IC Design Education Center (IDEC).

-PublicationJoon-Kyu Han, Sung-Yool Choi, Yang-Kyu Choi, et al.“Cointegration of single-transistor neurons and synapses by nanoscale CMOS fabrication for highly scalable neuromorphic hardware,” Science Advances (DOI: 10.1126/sciadv.abg8836)

-ProfileProfessor Yang-Kyu ChoiNano-Oriented Bio-Electronics Labhttps://sites.google.com/view/nobelab/

School of Electrical EngineeringKAIST

Professor Sung-Yool ChoiMolecular and Nano Device Laboratoryhttps://www.mndl.kaist.ac.kr/

School of Electrical EngineeringKAIST

2021.08.05 View 11458