research

Forming reliable multi-level metal interconnections is a key technology for integrating devices into organic integrated circuits (ICs). The conventional approach, called “via-hole,” locally removes the insulator and utilizes metal interconnects through the holes. Due to the high sensitivity of organic materials to chemical solvents, heat, and photo-radiation used in conventional “via-hole” methods, alternative printing methods or laser drilling methods have been developed. However, finding a reliable and practical metal interconnection for organic ICs is still challenging.

The research team of KAIST Professor Sung Gap Im and Postech Professor Kim Jae-Joon reported a new interconnection method that does not require via-hole formation, “via-hole-less metal interconnection,” in Nature Communications on June 3.

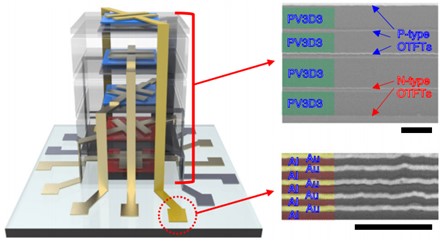

Metal electrodes in different layers can be isolated from each other by patterned dielectric layers, where they then can be interconnected to others in the open area where the dielectric layer is not present. See the images below. Vapor phase deposition and in-situ patterning of dielectric layer using iCVD (initiated chemical vapor deposition), used in the “via-hole-less” method, ensure a damage-free process for organic semiconductor materials and result in outstanding performance of the organic devices as multilevel metal interconnects are reliably formed. The team successfully demonstrated three-dimensional (3D) stacking of five organic transistors and integrated circuits using the proposed via-hole-less interconnect method. See the image below.

Vapor phase deposition and in-situ patterning of dielectric layer using iCVD (initiated chemical vapor deposition), used in the “via-hole-less” method, ensure a damage-free process for organic semiconductor materials and result in outstanding performance of the organic devices as multilevel metal interconnects are reliably formed. The team successfully demonstrated three-dimensional (3D) stacking of five organic transistors and integrated circuits using the proposed via-hole-less interconnect method. See the image below.

Professor Kim explained, “Our proposed via-hole-less interconnect method using a selectively patterned dielectric overcomes the limitations of the previous time-consuming, one-by-one via-hole formation process and provides reliable methods for creating metal interconnects in organic ICs. We expect the via-hole-less scheme to bring advances to organic IC technology.”

-

event A heated battle of science and sports, who is the winner of this year's KA-PO War?

< Photos from KAIST-POSTECH Science War (photographed by Student Junhyeok Park of KAIST Freshman Course) > The future leaders of science at KAIST and POSTECH (President Seong Keun Kim) held their annual science and sporting event at POSTECH for two days from September 20th to 21st. The 'KAIST-POSTECH Science War (hereafter KA-PO War)' is a festival consisting of science and sports games and various side events to promote exchange and cooperation between the two universities. It is als

2024-09-19 -

research Slippery When Wet: Fish and Seaweed Inspire Ships to Reduce Fluid Friction

Faster ships could be on the horizon after KAIST scientists develop a slippery surface inspired by fish and seaweed to reduce the hull's drag through the water. Long-distance cargo ships lose a significant amount of energy due to fluid friction. Looking to the drag reduction mechanisms employed by aquatic life can provide inspiration on how to improve efficiency. Fish and seaweed secrete a layer of mucus to create a slippery surface, reducing their friction as they travel through water. A pote

2020-10-12 -

research Hierarchical Porous Titanium Nitride Synthesized by Multiscale Phase Separation for LSBs

(from left: Professor Jinwoo Lee and PhD candidate Won-Gwang Lim) A KAIST research team developed ultra-stable, high-rate lithium-sulfur batteries (LSBs) by using hierarchical porous titanium nitride as a sulfur host, and achieved superior cycle stability and high rate performance for LSBs. The control of large amounts of energy is required for use in an electric vehicle or smart grid system. In this sense, the development of next-generation secondary batteries is in high

2019-01-28 -

research Rh Ensemble Catalyst for Effective Automobile Exhaust Treatment

(from left: Professor Hyunjoo Lee and PhD candidate Hojin Jeong) A KAIST research team has developed a fully dispersed Rh ensemble catalyst (ENS) that shows better performance than commercial diesel oxidation catalyst (DOC). This newly developed ENSs could improve low-temperature automobile exhaust treatment. Precious metals have been used for various heterogeneous reactions, but it is crucial to maximize efficiency of catalysts due to their high cost. Single-atom catalys

2018-08-29 -

event JETS Conference 2017

KAIST and four science and technology research universities in Korea co-hosted a technology start-up fair, the 2017 JETS (Job, Exhibition, Tech Forum, and Startup) Conference January 19 ~20 in the Ryu Geun-chul Sports Complex at KAIST. Korea’s major science and technology research universities, Daegu Gyeongbuk Institute of Science and Technology (DGIST), Gwangju Institute of Science and Technology (GIST), Pohang University of Science and Technology (Postech), and Ulsan National Inst

2017-01-20