Integrated+circuit

-

Novel Via-Hole-Less Multilevel Metal Interconnection Methods

Forming reliable multi-level metal interconnections is a key technology for integrating devices into organic integrated circuits (ICs). The conventional approach, called “via-hole,” locally removes the insulator and utilizes metal interconnects through the holes. Due to the high sensitivity of organic materials to chemical solvents, heat, and photo-radiation used in conventional “via-hole” methods, alternative printing methods or laser drilling methods have been developed. However, finding a reliable and practical metal interconnection for organic ICs is still challenging.

The research team of KAIST Professor Sung Gap Im and Postech Professor Kim Jae-Joon reported a new interconnection method that does not require via-hole formation, “via-hole-less metal interconnection,” in Nature Communications on June 3.

Metal electrodes in different layers can be isolated from each other by patterned dielectric layers, where they then can be interconnected to others in the open area where the dielectric layer is not present. See the images below. Vapor phase deposition and in-situ patterning of dielectric layer using iCVD (initiated chemical vapor deposition), used in the “via-hole-less” method, ensure a damage-free process for organic semiconductor materials and result in outstanding performance of the organic devices as multilevel metal interconnects are reliably formed. The team successfully demonstrated three-dimensional (3D) stacking of five organic transistors and integrated circuits using the proposed via-hole-less interconnect method. See the image below.

Vapor phase deposition and in-situ patterning of dielectric layer using iCVD (initiated chemical vapor deposition), used in the “via-hole-less” method, ensure a damage-free process for organic semiconductor materials and result in outstanding performance of the organic devices as multilevel metal interconnects are reliably formed. The team successfully demonstrated three-dimensional (3D) stacking of five organic transistors and integrated circuits using the proposed via-hole-less interconnect method. See the image below.

Professor Kim explained, “Our proposed via-hole-less interconnect method using a selectively patterned dielectric overcomes the limitations of the previous time-consuming, one-by-one via-hole formation process and provides reliable methods for creating metal interconnects in organic ICs. We expect the via-hole-less scheme to bring advances to organic IC technology.”

2019.06.18 View 44342

Novel Via-Hole-Less Multilevel Metal Interconnection Methods

Forming reliable multi-level metal interconnections is a key technology for integrating devices into organic integrated circuits (ICs). The conventional approach, called “via-hole,” locally removes the insulator and utilizes metal interconnects through the holes. Due to the high sensitivity of organic materials to chemical solvents, heat, and photo-radiation used in conventional “via-hole” methods, alternative printing methods or laser drilling methods have been developed. However, finding a reliable and practical metal interconnection for organic ICs is still challenging.

The research team of KAIST Professor Sung Gap Im and Postech Professor Kim Jae-Joon reported a new interconnection method that does not require via-hole formation, “via-hole-less metal interconnection,” in Nature Communications on June 3.

Metal electrodes in different layers can be isolated from each other by patterned dielectric layers, where they then can be interconnected to others in the open area where the dielectric layer is not present. See the images below. Vapor phase deposition and in-situ patterning of dielectric layer using iCVD (initiated chemical vapor deposition), used in the “via-hole-less” method, ensure a damage-free process for organic semiconductor materials and result in outstanding performance of the organic devices as multilevel metal interconnects are reliably formed. The team successfully demonstrated three-dimensional (3D) stacking of five organic transistors and integrated circuits using the proposed via-hole-less interconnect method. See the image below.

Vapor phase deposition and in-situ patterning of dielectric layer using iCVD (initiated chemical vapor deposition), used in the “via-hole-less” method, ensure a damage-free process for organic semiconductor materials and result in outstanding performance of the organic devices as multilevel metal interconnects are reliably formed. The team successfully demonstrated three-dimensional (3D) stacking of five organic transistors and integrated circuits using the proposed via-hole-less interconnect method. See the image below.

Professor Kim explained, “Our proposed via-hole-less interconnect method using a selectively patterned dielectric overcomes the limitations of the previous time-consuming, one-by-one via-hole formation process and provides reliable methods for creating metal interconnects in organic ICs. We expect the via-hole-less scheme to bring advances to organic IC technology.”

2019.06.18 View 44342 -

Continuous Roll-Process Technology for Transferring and Packaging Flexible Large-Scale Integrated Circuits

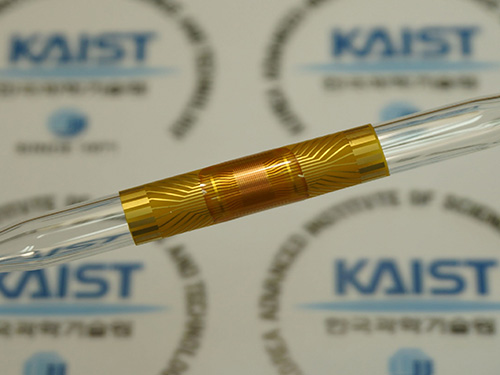

A research team led by Professor Keon Jae Lee from KAIST and by Dr. Jae-Hyun Kim from the Korea Institute of Machinery and Materials (KIMM) has jointly developed a continuous roll-processing technology that transfers and packages flexible large-scale integrated circuits (LSI), the key element in constructing the computer’s brain such as CPU, on plastics to realize flexible electronics.

Professor Lee previously demonstrated the silicon-based flexible LSIs using 0.18 CMOS (complementary metal-oxide semiconductor) process in 2013 (ACS Nano, “In Vivo Silicon-based Flexible Radio Frequency Integrated Circuits Monolithically Encapsulated with Biocompatible Liquid Crystal Polymers”) and presented the work in an invited talk of 2015 International Electron Device Meeting (IEDM), the world’s premier semiconductor forum.

Highly productive roll-processing is considered a core technology for accelerating the commercialization of wearable computers using flexible LSI. However, realizing it has been a difficult challenge not only from the roll-based manufacturing perspective but also for creating roll-based packaging for the interconnection of flexible LSI with flexible displays, batteries, and other peripheral devices.

To overcome these challenges, the research team started fabricating NAND flash memories on a silicon wafer using conventional semiconductor processes, and then removed a sacrificial wafer leaving a top hundreds-nanometer-thick circuit layer. Next, they simultaneously transferred and interconnected the ultrathin device on a flexible substrate through the continuous roll-packaging technology using anisotropic conductive film (ACF). The final silicon-based flexible NAND memory successfully demonstrated stable memory operations and interconnections even under severe bending conditions. This roll-based flexible LSI technology can be potentially utilized to produce flexible application processors (AP), high-density memories, and high-speed communication devices for mass manufacture.

Professor Lee said, “Highly productive roll-process was successfully applied to flexible LSIs to continuously transfer and interconnect them onto plastics. For example, we have confirmed the reliable operation of our flexible NAND memory at the circuit level by programming and reading letters in ASCII codes. Out results may open up new opportunities to integrate silicon-based flexible LSIs on plastics with the ACF packing for roll-based manufacturing.”

Dr. Kim added, “We employed the roll-to-plate ACF packaging, which showed outstanding bonding capability for continuous roll-based transfer and excellent flexibility of interconnecting core and peripheral devices. This can be a key process to the new era of flexible computers combining the already developed flexible displays and batteries.”

The team’s results will be published on the front cover of Advanced Materials (August 31, 2016) in an article entitled “Simultaneous Roll Transfer and Interconnection of Silicon NAND Flash Memory.” (DOI: 10.1002/adma.201602339)

YouTube Link: https://www.youtube.com/watch?v=8OJjAEm27sw

Picture 1: This schematic image shows the flexible silicon NAND flash memory produced by the simultaneous roll-transfer and interconnection process.

Picture 2: The flexible silicon NAND flash memory is attached to a 7 mm diameter glass rod.

2016.09.01 View 11804

Continuous Roll-Process Technology for Transferring and Packaging Flexible Large-Scale Integrated Circuits

A research team led by Professor Keon Jae Lee from KAIST and by Dr. Jae-Hyun Kim from the Korea Institute of Machinery and Materials (KIMM) has jointly developed a continuous roll-processing technology that transfers and packages flexible large-scale integrated circuits (LSI), the key element in constructing the computer’s brain such as CPU, on plastics to realize flexible electronics.

Professor Lee previously demonstrated the silicon-based flexible LSIs using 0.18 CMOS (complementary metal-oxide semiconductor) process in 2013 (ACS Nano, “In Vivo Silicon-based Flexible Radio Frequency Integrated Circuits Monolithically Encapsulated with Biocompatible Liquid Crystal Polymers”) and presented the work in an invited talk of 2015 International Electron Device Meeting (IEDM), the world’s premier semiconductor forum.

Highly productive roll-processing is considered a core technology for accelerating the commercialization of wearable computers using flexible LSI. However, realizing it has been a difficult challenge not only from the roll-based manufacturing perspective but also for creating roll-based packaging for the interconnection of flexible LSI with flexible displays, batteries, and other peripheral devices.

To overcome these challenges, the research team started fabricating NAND flash memories on a silicon wafer using conventional semiconductor processes, and then removed a sacrificial wafer leaving a top hundreds-nanometer-thick circuit layer. Next, they simultaneously transferred and interconnected the ultrathin device on a flexible substrate through the continuous roll-packaging technology using anisotropic conductive film (ACF). The final silicon-based flexible NAND memory successfully demonstrated stable memory operations and interconnections even under severe bending conditions. This roll-based flexible LSI technology can be potentially utilized to produce flexible application processors (AP), high-density memories, and high-speed communication devices for mass manufacture.

Professor Lee said, “Highly productive roll-process was successfully applied to flexible LSIs to continuously transfer and interconnect them onto plastics. For example, we have confirmed the reliable operation of our flexible NAND memory at the circuit level by programming and reading letters in ASCII codes. Out results may open up new opportunities to integrate silicon-based flexible LSIs on plastics with the ACF packing for roll-based manufacturing.”

Dr. Kim added, “We employed the roll-to-plate ACF packaging, which showed outstanding bonding capability for continuous roll-based transfer and excellent flexibility of interconnecting core and peripheral devices. This can be a key process to the new era of flexible computers combining the already developed flexible displays and batteries.”

The team’s results will be published on the front cover of Advanced Materials (August 31, 2016) in an article entitled “Simultaneous Roll Transfer and Interconnection of Silicon NAND Flash Memory.” (DOI: 10.1002/adma.201602339)

YouTube Link: https://www.youtube.com/watch?v=8OJjAEm27sw

Picture 1: This schematic image shows the flexible silicon NAND flash memory produced by the simultaneous roll-transfer and interconnection process.

Picture 2: The flexible silicon NAND flash memory is attached to a 7 mm diameter glass rod.

2016.09.01 View 11804 -

The 2014 SoC Robot Competition Took Place

Professor Hoi-Jun Yoo of the Department of Electrical Engineering at KAIST and his research team hosted a competition for miniature robots with artificial intelligence at KINTEX in Ilsan, Korea, on October 23-26, 2014.

The competition, called the 2014 SoC Robot War, showed the latest developments of semiconductor and robot technology through the robots’ presentations of the Korean martial art, Taekwondo, and hurdles race. SoC is a system on ship, an integrated circuit that holds all components of a computer or other electronic systems in a single chip. SoC robots are equipped with an artificial intelligence system, and therefore, can recognize things on their own or respond automatically to environmental changes. SoC robots are developed with the integration of semiconductor technology and robotics engineering.

Marking the thirteenth competition this year since its inception, the Robot War featured two competitions between HURO and Taekwon Robots. Under the HURO competition, participating robots were required to run a hurdle race, pass through barricades, and cross a bridge. The winning team received an award from the president of the Republic of Korea. Robots participating in the Taekwon Robot competition performed some of the main movements of Taekwondo such as front and side kicks and fist techniques. The winning team received an award from the prime minster of the Republic of Korea.

A total of 105 teams with 530 students and researchers from different universities across the country participated in preliminaries, and 30 teams qualified for the final competition.

2014.10.27 View 9002

The 2014 SoC Robot Competition Took Place

Professor Hoi-Jun Yoo of the Department of Electrical Engineering at KAIST and his research team hosted a competition for miniature robots with artificial intelligence at KINTEX in Ilsan, Korea, on October 23-26, 2014.

The competition, called the 2014 SoC Robot War, showed the latest developments of semiconductor and robot technology through the robots’ presentations of the Korean martial art, Taekwondo, and hurdles race. SoC is a system on ship, an integrated circuit that holds all components of a computer or other electronic systems in a single chip. SoC robots are equipped with an artificial intelligence system, and therefore, can recognize things on their own or respond automatically to environmental changes. SoC robots are developed with the integration of semiconductor technology and robotics engineering.

Marking the thirteenth competition this year since its inception, the Robot War featured two competitions between HURO and Taekwon Robots. Under the HURO competition, participating robots were required to run a hurdle race, pass through barricades, and cross a bridge. The winning team received an award from the president of the Republic of Korea. Robots participating in the Taekwon Robot competition performed some of the main movements of Taekwondo such as front and side kicks and fist techniques. The winning team received an award from the prime minster of the Republic of Korea.

A total of 105 teams with 530 students and researchers from different universities across the country participated in preliminaries, and 30 teams qualified for the final competition.

2014.10.27 View 9002 -

Green Technology for Data Centers: Ultra-low Power 100 Gbps Ethernet Integrated Circuit Developed

A new integrated circuit (IC), consuming only 0.75W of electricity, will reduce the power usage of data chips installed at data centers by one-third.

Each day, billions of people surf the Internet for information, entertainment, and educational content. The Internet contains an immeasurable amount of information and knowledge generated every minute all around the world that is readily available to everyone with a click of a computer mouse. The real magic of the Internet, however, lies in data centers, where hundreds of billions of data are stored and distributed to designated users around the clock.

Today, almost every business or organization either has its own data centers or outsources data center services to a third party. These centers house highly specialized equipment responsible for the support of computers, networks, data storage, and business security. Accordingly, the operational cost of data centers is tremendous because they consume a large amount of electricity.

Data centers can consume up to 100 times more energy than a standard office building. Data center energy consumption doubled from 2000 to 2006, reaching more than 60 billion kilowatt hours per year. If the current usage and technology trends continue, the energy consumption of data centers in the US will reach 8% of the country’s total electric power consumption by 2020.

A research team at the Korea Advanced Institute of Science and Technology (KAIST) and Terasquare, Inc. (

http://www.terasquare.co.kr

), a spin-off company of the university,

developed an extremely low-powered integrated circuit for Ethernet that consumes less than 0.75W of electricity but is able to send and receive data at the high speed of 100 gigabits per second (Gbps). The research team, headed by Hyeon-Min Bae, assistant professor of electrical engineering at KAIST, claims that the new microchip uses only one-third of the electricity consumed by the currently installed chips at data centers, thereby helping the centers to save energy.

Integrated circuits are embedded on communication modules that are inserted into a line card. Data centers have numerous line cards to build a network including routers and switches. Currently, 8W ICs are the most common in the market, and they consume a lot of energy and require the largest modules (112 cm

2

of CFP), decreasing the port density of line cards and, thus, limiting the amount of data transmission.

The ultra-low-power-circuit, 100-gigabit, full-transceiver CDR, is the world’s first solution that can be loaded to the smallest communication modules (20 cm

2

of CFP4 or 16 cm

2

of

QSFP28), the next-generation chips for data centers. Compared with other chip producers, the 100 Gbps CDR is a greener version of the technology that improves the energy efficiency of data centers while maintaining the high speed of data transmission.

Professor Hyeon-Min Bae said, “When we demonstrate our chip in September of this year at one of the leading companies that manufacture optical communication components and systems, they said that our product is two years ahead of those of our competitors. We plan to produce the chip from 2014 and expect that it will lead the 100 Gbps Ethernet IC market, which is expected to grow to USD 1 billion by 2017.”

The commercial model of the IC was first introduced at the 39

th

European Conference and Exhibition on Optical Communication (ECOC), the largest optical communication forum for new results and developments in Europe, held from September 22-26 at ExCeL London, an international exhibition and convention center.

Professor Bae added, “We received positive responses to our ultra-low-power 100-Gbps Ethernet IC at the ECOC. The chip will be used not only for a particular industry but also for many of next-generation, super-high-speed information communications technologies, such as high-speed USB, high-definition multimedia interface (HDMI), and TV interface.”

Before joining KAIST, Hyeon-Min Bae worked for many years at Finisar as a researcher who designed and developed the world’s first super-high-speed circuit, the 100 Gbps Ethernet IC.

2013.11.25 View 9861

Green Technology for Data Centers: Ultra-low Power 100 Gbps Ethernet Integrated Circuit Developed

A new integrated circuit (IC), consuming only 0.75W of electricity, will reduce the power usage of data chips installed at data centers by one-third.

Each day, billions of people surf the Internet for information, entertainment, and educational content. The Internet contains an immeasurable amount of information and knowledge generated every minute all around the world that is readily available to everyone with a click of a computer mouse. The real magic of the Internet, however, lies in data centers, where hundreds of billions of data are stored and distributed to designated users around the clock.

Today, almost every business or organization either has its own data centers or outsources data center services to a third party. These centers house highly specialized equipment responsible for the support of computers, networks, data storage, and business security. Accordingly, the operational cost of data centers is tremendous because they consume a large amount of electricity.

Data centers can consume up to 100 times more energy than a standard office building. Data center energy consumption doubled from 2000 to 2006, reaching more than 60 billion kilowatt hours per year. If the current usage and technology trends continue, the energy consumption of data centers in the US will reach 8% of the country’s total electric power consumption by 2020.

A research team at the Korea Advanced Institute of Science and Technology (KAIST) and Terasquare, Inc. (

http://www.terasquare.co.kr

), a spin-off company of the university,

developed an extremely low-powered integrated circuit for Ethernet that consumes less than 0.75W of electricity but is able to send and receive data at the high speed of 100 gigabits per second (Gbps). The research team, headed by Hyeon-Min Bae, assistant professor of electrical engineering at KAIST, claims that the new microchip uses only one-third of the electricity consumed by the currently installed chips at data centers, thereby helping the centers to save energy.

Integrated circuits are embedded on communication modules that are inserted into a line card. Data centers have numerous line cards to build a network including routers and switches. Currently, 8W ICs are the most common in the market, and they consume a lot of energy and require the largest modules (112 cm

2

of CFP), decreasing the port density of line cards and, thus, limiting the amount of data transmission.

The ultra-low-power-circuit, 100-gigabit, full-transceiver CDR, is the world’s first solution that can be loaded to the smallest communication modules (20 cm

2

of CFP4 or 16 cm

2

of

QSFP28), the next-generation chips for data centers. Compared with other chip producers, the 100 Gbps CDR is a greener version of the technology that improves the energy efficiency of data centers while maintaining the high speed of data transmission.

Professor Hyeon-Min Bae said, “When we demonstrate our chip in September of this year at one of the leading companies that manufacture optical communication components and systems, they said that our product is two years ahead of those of our competitors. We plan to produce the chip from 2014 and expect that it will lead the 100 Gbps Ethernet IC market, which is expected to grow to USD 1 billion by 2017.”

The commercial model of the IC was first introduced at the 39

th

European Conference and Exhibition on Optical Communication (ECOC), the largest optical communication forum for new results and developments in Europe, held from September 22-26 at ExCeL London, an international exhibition and convention center.

Professor Bae added, “We received positive responses to our ultra-low-power 100-Gbps Ethernet IC at the ECOC. The chip will be used not only for a particular industry but also for many of next-generation, super-high-speed information communications technologies, such as high-speed USB, high-definition multimedia interface (HDMI), and TV interface.”

Before joining KAIST, Hyeon-Min Bae worked for many years at Finisar as a researcher who designed and developed the world’s first super-high-speed circuit, the 100 Gbps Ethernet IC.

2013.11.25 View 9861 -

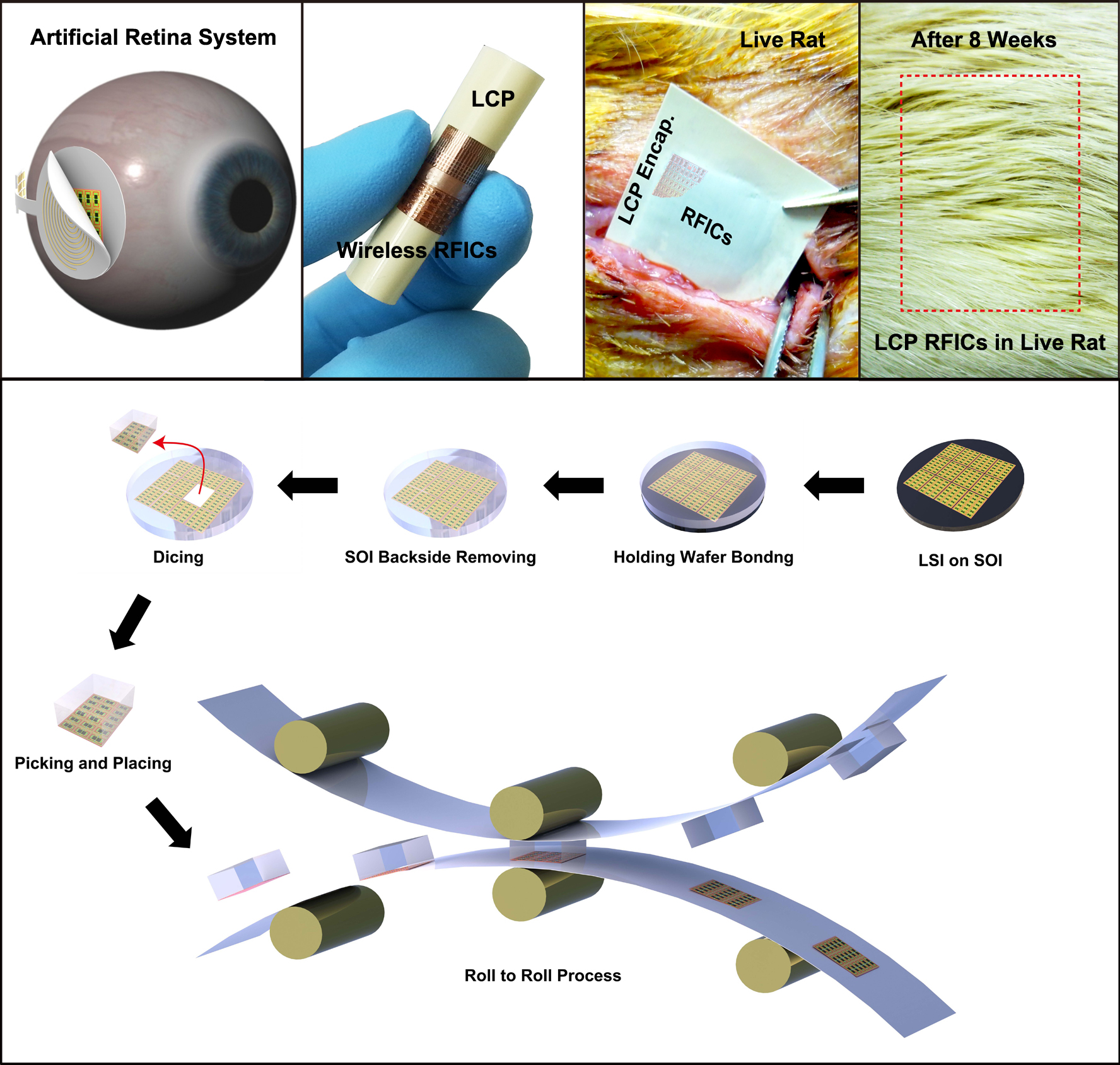

A KAIST research team developed in vivo flexible large scale integrated circuits

Daejeon, Republic of Korea, May 6th, 2013–-A team led by Professor Keon Jae Lee from the Department of Materials Science and Engineering at KAIST has developed in vivo silicon-based flexible large scale integrated circuits (LSI) for bio-medical wireless communication.

Silicon-based semiconductors have played significant roles in signal processing, nerve stimulation, memory storage, and wireless communication in implantable electronics. However, the rigid and bulky LSI chips have limited uses in in vivo devices due to incongruent contact with the curvilinear surfaces of human organs. Especially, artificial retinas recently approved by the Food and Drug Administration (refer to the press release of FDA"s artificial retina approval) require extremely flexible and slim LSI to incorporate it within the cramped area of the human eye.

Although several research teams have fabricated flexible integrated circuits (ICs, tens of interconnected transistors) on plastics, their inaccurate nano-scale alignment on plastics has restricted the demonstration of flexible nano-transistors and their large scale interconnection for in vivo LSI applications such as main process unit (MPU), high density memory and wireless communication. Professor Lee"s team previously demonstrated fully functional flexible memory using ultrathin silicon membranes (Nano Letters, Flexible Memristive Memory Array on Plastic Substrates), however, its integration level and transistor size (over micron scale) have limited functional applications for flexible consumer electronics.

Professor Keon Jae Lee"s team fabricated radio frequency integrated circuits (RFICs) interconnected with thousand nano-transistors on silicon wafer by state-of-the-art CMOS process, and then they removed the entire bottom substrate except top 100 nm active circuit layer by wet chemical etching. The flexible RF switches for wireless communication were monolithically encapsulated with biocompatible liquid crystal polymers (LCPs) for in vivo bio-medical applications. Finally, they implanted the LCP encapsulated RFICs into live rats to demonstrate the stable operation of flexible devices under in vivo circumstances.

Professor Lee said, "This work could provide an approach to flexible LSI for an ideal artificial retina system and other bio-medical devices. Moreover, the result represents an exciting technology with the strong potential to realize fully flexible consumer electronics such as application processor (AP) for mobile operating system, high-capacity memory, and wireless communication in the near future."

This result was published in the May online issue of the American Chemical Society"s journal, ACS Nano (In vivo Flexible RFICs Monolithically Encapsulated with LCP). They are currently engaged in commercializing efforts of roll-to-roll printing of flexible LSI on large area plastic substrates.

Movie at Youtube Link: Fabrication process for flexible LSI for flexible display, wearable computer and artificial retina for in vivo biomedical application

http://www.youtube.com/watch?v=5PpbM7m2PPs&feature=youtu.be

Applications of in Vivo Flexible Large Scale Integrated Circuits

Top: In vivo flexible large scale integrated circuits (LSI); Bottom: Schematic of roll-to-roll printing of flexible LSI on large area plastics.

2013.06.09 View 14332

A KAIST research team developed in vivo flexible large scale integrated circuits

Daejeon, Republic of Korea, May 6th, 2013–-A team led by Professor Keon Jae Lee from the Department of Materials Science and Engineering at KAIST has developed in vivo silicon-based flexible large scale integrated circuits (LSI) for bio-medical wireless communication.

Silicon-based semiconductors have played significant roles in signal processing, nerve stimulation, memory storage, and wireless communication in implantable electronics. However, the rigid and bulky LSI chips have limited uses in in vivo devices due to incongruent contact with the curvilinear surfaces of human organs. Especially, artificial retinas recently approved by the Food and Drug Administration (refer to the press release of FDA"s artificial retina approval) require extremely flexible and slim LSI to incorporate it within the cramped area of the human eye.

Although several research teams have fabricated flexible integrated circuits (ICs, tens of interconnected transistors) on plastics, their inaccurate nano-scale alignment on plastics has restricted the demonstration of flexible nano-transistors and their large scale interconnection for in vivo LSI applications such as main process unit (MPU), high density memory and wireless communication. Professor Lee"s team previously demonstrated fully functional flexible memory using ultrathin silicon membranes (Nano Letters, Flexible Memristive Memory Array on Plastic Substrates), however, its integration level and transistor size (over micron scale) have limited functional applications for flexible consumer electronics.

Professor Keon Jae Lee"s team fabricated radio frequency integrated circuits (RFICs) interconnected with thousand nano-transistors on silicon wafer by state-of-the-art CMOS process, and then they removed the entire bottom substrate except top 100 nm active circuit layer by wet chemical etching. The flexible RF switches for wireless communication were monolithically encapsulated with biocompatible liquid crystal polymers (LCPs) for in vivo bio-medical applications. Finally, they implanted the LCP encapsulated RFICs into live rats to demonstrate the stable operation of flexible devices under in vivo circumstances.

Professor Lee said, "This work could provide an approach to flexible LSI for an ideal artificial retina system and other bio-medical devices. Moreover, the result represents an exciting technology with the strong potential to realize fully flexible consumer electronics such as application processor (AP) for mobile operating system, high-capacity memory, and wireless communication in the near future."

This result was published in the May online issue of the American Chemical Society"s journal, ACS Nano (In vivo Flexible RFICs Monolithically Encapsulated with LCP). They are currently engaged in commercializing efforts of roll-to-roll printing of flexible LSI on large area plastic substrates.

Movie at Youtube Link: Fabrication process for flexible LSI for flexible display, wearable computer and artificial retina for in vivo biomedical application

http://www.youtube.com/watch?v=5PpbM7m2PPs&feature=youtu.be

Applications of in Vivo Flexible Large Scale Integrated Circuits

Top: In vivo flexible large scale integrated circuits (LSI); Bottom: Schematic of roll-to-roll printing of flexible LSI on large area plastics.

2013.06.09 View 14332 -

KAIST develops a low-power 60 GHz radio frequency chip for mobile devices

As the capacity of handheld devices increases to accommodate a greater number of functions, these devices have more memory, larger display screens, and the ability to play higher definition video files. If the users of mobile devices, including smartphones, tablet PCs, and notebooks, want to share or transfer data on one device with that of another device, a great deal of time and effort are needed.

As a possible method for the speedy transmission of large data, researchers are studying the adoption of gigabits per second (Gbps) wireless communications operating over the 60 gigahertz (GHz) frequency band. Some commercial approaches have been introduced for full-HD video streaming from a fixed source to a display by using the 60 GHz band. But mobile applications have not been developed yet because the 60 GHz radio frequency (RF) circuit consumes hundreds of milliwatts (mW) of DC power.

Professor Chul Soon Park from the Department of Electrical Engineering at the Korea Advanced Institute of Science and Technology (KAIST) and his research team recently developed a low-power version of the 60 GHz radio frequency integrated circuit (RFIC). Inside the circuit are an energy-efficient modulator performing amplification as well as modulation and a sensitivity-improved receiver employing a gain boosting demodulator.

The research team said that their RFIC draws as little as 67 mW of power in the 60 GHz frequency band, consuming 31mW to send and 36mW to receive large volumes of data. RFIC is also small enough to be mounted on smartphones or notebooks, requiring only one chip (its width, length, and height are about 1 mm) and one antenna (4x5x1 mm3) for sending and receiving data with an integrated switch.

Professor Park, Director of the Intelligent Radio Engineering Center at KAIST, gave an upbeat assessment of the potential of RFIC for future applications. What we have developed is a low-power 60-GHz RF chip with a transmission speed of 10.7 gigabits per second. In tests, we were able to stream uncompressed full-HD videos from a smartphone or notebook to a display without a cable connection (Youtube Link: http://www.youtube.com/watch?v=6PVSLBhMymc). Our chip can be installed on mobile devices or even on cameras so that the devices are virtually connected to other devices and able to exchange large data with each other."

2013.04.02 View 9040

KAIST develops a low-power 60 GHz radio frequency chip for mobile devices

As the capacity of handheld devices increases to accommodate a greater number of functions, these devices have more memory, larger display screens, and the ability to play higher definition video files. If the users of mobile devices, including smartphones, tablet PCs, and notebooks, want to share or transfer data on one device with that of another device, a great deal of time and effort are needed.

As a possible method for the speedy transmission of large data, researchers are studying the adoption of gigabits per second (Gbps) wireless communications operating over the 60 gigahertz (GHz) frequency band. Some commercial approaches have been introduced for full-HD video streaming from a fixed source to a display by using the 60 GHz band. But mobile applications have not been developed yet because the 60 GHz radio frequency (RF) circuit consumes hundreds of milliwatts (mW) of DC power.

Professor Chul Soon Park from the Department of Electrical Engineering at the Korea Advanced Institute of Science and Technology (KAIST) and his research team recently developed a low-power version of the 60 GHz radio frequency integrated circuit (RFIC). Inside the circuit are an energy-efficient modulator performing amplification as well as modulation and a sensitivity-improved receiver employing a gain boosting demodulator.

The research team said that their RFIC draws as little as 67 mW of power in the 60 GHz frequency band, consuming 31mW to send and 36mW to receive large volumes of data. RFIC is also small enough to be mounted on smartphones or notebooks, requiring only one chip (its width, length, and height are about 1 mm) and one antenna (4x5x1 mm3) for sending and receiving data with an integrated switch.

Professor Park, Director of the Intelligent Radio Engineering Center at KAIST, gave an upbeat assessment of the potential of RFIC for future applications. What we have developed is a low-power 60-GHz RF chip with a transmission speed of 10.7 gigabits per second. In tests, we were able to stream uncompressed full-HD videos from a smartphone or notebook to a display without a cable connection (Youtube Link: http://www.youtube.com/watch?v=6PVSLBhMymc). Our chip can be installed on mobile devices or even on cameras so that the devices are virtually connected to other devices and able to exchange large data with each other."

2013.04.02 View 9040