%EB%B0%98%EB%8F%84%EC%B2%B4

-

KAIST-삼성전자, 시스템 반도체 칩 추가 지원 협약 체결

우리 대학이 삼성전자와 ‘130nm BCDMOS 공정 지원' 협약을 23일 오후 체결한다.

삼성전자가 반도체 설계 전문 인재 양성을 위해 지원하는 BCDMOS(복합고전압소자: Bipolar-CMOS-DMOS)*는 고전압과 고속 동작이 필요한 전력 관리 응용 분야에 적합한 공정이다.

이번 협약을 바탕으로 130nm(나노미터) BCDMOS 8인치 공정을 올해 하반기부터 도입해 국내 반도체 전공 석·박사 과정 학생에게 칩 제작 기회를 제공한다.

이를 위해, 우리 대학 반도체설계교육센터(소장 박인철, IC Design Education Center 이하 IDEC)는 130nm BCDMOS 공정을 위한 설계 전자설계자동화툴(EDA Tool)과 기술 지원 환경을 마련했다.

IDEC은 삼성전자와 협력해 2021년부터 28nm 로직** 공정 칩 제작 기회를 학생들에게 제공하고 있으며, 지난해 28nm FD-SOI***공정 지원도 추가했다.

올해 제공된 28nm 공정에는 30개 대학 160개 팀, 800여 명의 학생이 설계에 참여해 칩을 제작 중이다. 이번 협약으로 추가된 130nm BCDMOS 공정에는 올해 하반기 20개 팀을 시작으로 내년부터 2년간 상하반기 각 20개 팀이 칩 제작에 참여할 수 있게 됐다. 반도체 칩 제작은 대학원생들이 이론으로 설계한 도면을 실제 웨이퍼에 구현하여 실물을 만드는 중요한 과정이다. 실물 칩을 제작하면 설계의 정확성과 효율성을 검증할 수 있지만, 비용이 최소 3천만 원 이상 소요돼 학생들이 외부 지원 없이 칩 제작을 경험하기는 어려운 실정이다.

박인철 IDEC 소장은 “이번 삼성전자의 130nm BCDMOS 공정 지원은 해당 분야를 연구하는 대학에 실질적인 제작 기회를 제공해 연구 성과를 향상하는 데 크게 기여할 것으로 기대된다”라고 말했다.

이어, “특히 전력 관리와 고속 통신 분야에서 중요한 역할을 하는 공정으로 혁신적인 기술 개발로 이어질 수 있는 환경이 마련돼, 제작에 참여한 학생은 기술 개발의 경쟁력을 갖춘 전문 설계 인력으로 성장하게 될 것”이라고 덧붙였다.

23일 오후 우리 대학 IDEC 동탄교육장에서 열리는 협약식에는 박인철 소장과 박상훈 삼성전자 상무 등 양 기관의 주요 인사들이 참석한다. 협약식과 함께 2024년 하반기 130nm BCDMOS 공정에 참여하는 13개 대학의 19팀을 대상으로 설계설명회도 개최된다.

한편, KAIST IDEC은 1995년에 설립돼 시스템반도체 분야의 전문인력을 양성해왔다. 지난 29년간 삼성전자와 협력해 2천 219개 설계팀에 칩 제작 기회를 제공해 총 8천 1백여 명의 반도체 전문인력을 배출해 산업계와 학계의 발전을 도모했다.

2021년부터는 산업통상자원부의 '차세대 시스템반도체 설계 전문인력 양성 사업'을 수행하고 있으며, 2026년까지 정부 자금 170억을 지원받아 전국 대학 석·박사급 학생에게 반도체 칩 설계와 제작 환경을 제공할 계획이다.

양 기관은 이번 협약을 통해 두 기관은 반도체 전문 인력 양성을 위한 협력을 더욱 강화할 계획이다.

2024.07.24 조회수 630

KAIST-삼성전자, 시스템 반도체 칩 추가 지원 협약 체결

우리 대학이 삼성전자와 ‘130nm BCDMOS 공정 지원' 협약을 23일 오후 체결한다.

삼성전자가 반도체 설계 전문 인재 양성을 위해 지원하는 BCDMOS(복합고전압소자: Bipolar-CMOS-DMOS)*는 고전압과 고속 동작이 필요한 전력 관리 응용 분야에 적합한 공정이다.

이번 협약을 바탕으로 130nm(나노미터) BCDMOS 8인치 공정을 올해 하반기부터 도입해 국내 반도체 전공 석·박사 과정 학생에게 칩 제작 기회를 제공한다.

이를 위해, 우리 대학 반도체설계교육센터(소장 박인철, IC Design Education Center 이하 IDEC)는 130nm BCDMOS 공정을 위한 설계 전자설계자동화툴(EDA Tool)과 기술 지원 환경을 마련했다.

IDEC은 삼성전자와 협력해 2021년부터 28nm 로직** 공정 칩 제작 기회를 학생들에게 제공하고 있으며, 지난해 28nm FD-SOI***공정 지원도 추가했다.

올해 제공된 28nm 공정에는 30개 대학 160개 팀, 800여 명의 학생이 설계에 참여해 칩을 제작 중이다. 이번 협약으로 추가된 130nm BCDMOS 공정에는 올해 하반기 20개 팀을 시작으로 내년부터 2년간 상하반기 각 20개 팀이 칩 제작에 참여할 수 있게 됐다. 반도체 칩 제작은 대학원생들이 이론으로 설계한 도면을 실제 웨이퍼에 구현하여 실물을 만드는 중요한 과정이다. 실물 칩을 제작하면 설계의 정확성과 효율성을 검증할 수 있지만, 비용이 최소 3천만 원 이상 소요돼 학생들이 외부 지원 없이 칩 제작을 경험하기는 어려운 실정이다.

박인철 IDEC 소장은 “이번 삼성전자의 130nm BCDMOS 공정 지원은 해당 분야를 연구하는 대학에 실질적인 제작 기회를 제공해 연구 성과를 향상하는 데 크게 기여할 것으로 기대된다”라고 말했다.

이어, “특히 전력 관리와 고속 통신 분야에서 중요한 역할을 하는 공정으로 혁신적인 기술 개발로 이어질 수 있는 환경이 마련돼, 제작에 참여한 학생은 기술 개발의 경쟁력을 갖춘 전문 설계 인력으로 성장하게 될 것”이라고 덧붙였다.

23일 오후 우리 대학 IDEC 동탄교육장에서 열리는 협약식에는 박인철 소장과 박상훈 삼성전자 상무 등 양 기관의 주요 인사들이 참석한다. 협약식과 함께 2024년 하반기 130nm BCDMOS 공정에 참여하는 13개 대학의 19팀을 대상으로 설계설명회도 개최된다.

한편, KAIST IDEC은 1995년에 설립돼 시스템반도체 분야의 전문인력을 양성해왔다. 지난 29년간 삼성전자와 협력해 2천 219개 설계팀에 칩 제작 기회를 제공해 총 8천 1백여 명의 반도체 전문인력을 배출해 산업계와 학계의 발전을 도모했다.

2021년부터는 산업통상자원부의 '차세대 시스템반도체 설계 전문인력 양성 사업'을 수행하고 있으며, 2026년까지 정부 자금 170억을 지원받아 전국 대학 석·박사급 학생에게 반도체 칩 설계와 제작 환경을 제공할 계획이다.

양 기관은 이번 협약을 통해 두 기관은 반도체 전문 인력 양성을 위한 협력을 더욱 강화할 계획이다.

2024.07.24 조회수 630 -

“AI 반도체 미래가 밝다” KAIST PIM반도체설계연구센터, AI반도체 전문인력 양성 교육

과학기술정보통신부·정보통신기획평가원이 주관하는 PIM인공지능반도체 핵심기술개발사업의 지원을 받고있는 우리 대학 PIM반도체설계연구센터가 AI 반도체 전문인력 양성을 위해 전국 AI 및 반도체 관련 학과 학부생과 대학원생을 대상으로 SK하이닉스와 삼성전자의 PIM* 기반 이론 및 실습 교육을 진행했다. 강의는 6월 20일(목)부터 6월 21일(금)까지 SK하이닉스 교육, 7월 4일(목)부터 7월 5일(금)까지 삼성전자 교육을 각각 KAIST PIM반도체설계연구센터에서 진행했다.

*PIM(Processing-In-Memory): 메모리 반도체에 연산 기능을 추가하여 AI와 빅데이터 처리 분야에서 데이터 처리 속도를 높이면서도 사용 전력을 줄이는 반도체 설계 기술

이번 교육은 SK하이닉스의 AiM*과 삼성전자의 HBM-PIM*을 활용하여 수강생들이 직접 실습할 수 있는 기회를 제공했다. 전국 25개 대학교에서 300명이 넘는 학생들이 접수하여 높은 관심을 받았다.

* AiM(Accelerator-in-Memory): SK하이닉스의 PIM 반도체 제품명, GDDR6-AiM 포함

** HBM-PIM(Processing-in-Memory): 삼성전자의 PIM 반도체 제품명, 세계 최초로 메모리 반도체와 인공지능 프로세서를 결합한 제품

인공지능(AI) 시대에는 거대언어모델 등 방대한 데이터 처리 수요가 급증하면서 PIM 기술 도입의 필요성이 더욱 커지고 있다. 한국 반도체의 먹거리인 메모리 기술의 미래를 열어줄 PIM 연구 활성화를 위해, AI용 메모리 반도체 설계 및 응용 역량을 갖춘 실무 중심의 교육 프로그램을 마련했다.

강의는 ▲SK하이닉스의 'PIM을 사용한 LLM(거대언어모델)* 가속 환경에서의 활용', ▲삼성전자의 ‘AI 가속 환경에서 HBM과 HBM-PIM의 활용’을 주제로 진행했다. 또한 GPT의 등장으로 인한 환경 변화, 인공지능과 LLM에 대한 기본 지식, 챗봇 서비스 작용 원리 등이 다뤄졌다. 수강생들은 SK하이닉스의 AiM과 삼성전자의 HBM-PIM이 장착된 서버 환경에서 하드웨어를 직접 구동하여 실습했다.

* 거대언어모델(LLM, Large Language Model): 대량의 텍스트 데이터로 학습하는 인공지능으로 챗GPT가 이에 해당

PIM 반도체설계연구센터는 PIM 반도체 전문인력 양성을 위한 ‘PIM’ 교육 프로그램을 운영하고 있다. 연구 중심의 PIM 반도체 전문인력을 양성하여 한국 PIM 반도체 산업에 핵심 인력을 제공하는 것을 목표로 하고 있다. 교육 프로그램에 대한 자세한 내용은 PIM반도체설계연구센터 홈페이지에서 확인할 수 있다.

* PIM 반도체설계연구센터 홈페이지: https://ai-pim.org/

PIM반도체설계연구센터 유회준 센터장은 “이번 교육을 통해 산업 현장에서 실제로 어떻게 활용되는지 아는 것이 중요합니다. 특히, AI-PIM 반도체에 대한 관심이 높아짐에 따라 관련 교육 과정을 지속적으로 확대할 계획입니다. 이를 통해 참가자들이 최신 기술 동향을 따라잡고, 실무에 바로 적용할 수 있는 능력을 키울 수 있도록 하겠습니다.”라고 전했다.

우리 대학 전기및전자공학부 박사과정 엄소연 수강생은 “논문으로는 이해하기 어려웠던 내용을 실습을 통해 배울 수 있어 의미가 있었다. 특히, 실습 과정에서 얻은 경험과 통찰력은 앞으로 연구와 개발에 큰 도움이 될 것 같다.”라고 소감을 전했다.

수강생들은 질의응답 시간뿐만 아니라 쉬는 시간에도 강사에게 질문을 이어갔다. 미리 관련 논문을 읽고 온 학생들도 있어 PIM 반도체에 대한 열정을 확인할 수 있었다.

2024.07.11 조회수 946

“AI 반도체 미래가 밝다” KAIST PIM반도체설계연구센터, AI반도체 전문인력 양성 교육

과학기술정보통신부·정보통신기획평가원이 주관하는 PIM인공지능반도체 핵심기술개발사업의 지원을 받고있는 우리 대학 PIM반도체설계연구센터가 AI 반도체 전문인력 양성을 위해 전국 AI 및 반도체 관련 학과 학부생과 대학원생을 대상으로 SK하이닉스와 삼성전자의 PIM* 기반 이론 및 실습 교육을 진행했다. 강의는 6월 20일(목)부터 6월 21일(금)까지 SK하이닉스 교육, 7월 4일(목)부터 7월 5일(금)까지 삼성전자 교육을 각각 KAIST PIM반도체설계연구센터에서 진행했다.

*PIM(Processing-In-Memory): 메모리 반도체에 연산 기능을 추가하여 AI와 빅데이터 처리 분야에서 데이터 처리 속도를 높이면서도 사용 전력을 줄이는 반도체 설계 기술

이번 교육은 SK하이닉스의 AiM*과 삼성전자의 HBM-PIM*을 활용하여 수강생들이 직접 실습할 수 있는 기회를 제공했다. 전국 25개 대학교에서 300명이 넘는 학생들이 접수하여 높은 관심을 받았다.

* AiM(Accelerator-in-Memory): SK하이닉스의 PIM 반도체 제품명, GDDR6-AiM 포함

** HBM-PIM(Processing-in-Memory): 삼성전자의 PIM 반도체 제품명, 세계 최초로 메모리 반도체와 인공지능 프로세서를 결합한 제품

인공지능(AI) 시대에는 거대언어모델 등 방대한 데이터 처리 수요가 급증하면서 PIM 기술 도입의 필요성이 더욱 커지고 있다. 한국 반도체의 먹거리인 메모리 기술의 미래를 열어줄 PIM 연구 활성화를 위해, AI용 메모리 반도체 설계 및 응용 역량을 갖춘 실무 중심의 교육 프로그램을 마련했다.

강의는 ▲SK하이닉스의 'PIM을 사용한 LLM(거대언어모델)* 가속 환경에서의 활용', ▲삼성전자의 ‘AI 가속 환경에서 HBM과 HBM-PIM의 활용’을 주제로 진행했다. 또한 GPT의 등장으로 인한 환경 변화, 인공지능과 LLM에 대한 기본 지식, 챗봇 서비스 작용 원리 등이 다뤄졌다. 수강생들은 SK하이닉스의 AiM과 삼성전자의 HBM-PIM이 장착된 서버 환경에서 하드웨어를 직접 구동하여 실습했다.

* 거대언어모델(LLM, Large Language Model): 대량의 텍스트 데이터로 학습하는 인공지능으로 챗GPT가 이에 해당

PIM 반도체설계연구센터는 PIM 반도체 전문인력 양성을 위한 ‘PIM’ 교육 프로그램을 운영하고 있다. 연구 중심의 PIM 반도체 전문인력을 양성하여 한국 PIM 반도체 산업에 핵심 인력을 제공하는 것을 목표로 하고 있다. 교육 프로그램에 대한 자세한 내용은 PIM반도체설계연구센터 홈페이지에서 확인할 수 있다.

* PIM 반도체설계연구센터 홈페이지: https://ai-pim.org/

PIM반도체설계연구센터 유회준 센터장은 “이번 교육을 통해 산업 현장에서 실제로 어떻게 활용되는지 아는 것이 중요합니다. 특히, AI-PIM 반도체에 대한 관심이 높아짐에 따라 관련 교육 과정을 지속적으로 확대할 계획입니다. 이를 통해 참가자들이 최신 기술 동향을 따라잡고, 실무에 바로 적용할 수 있는 능력을 키울 수 있도록 하겠습니다.”라고 전했다.

우리 대학 전기및전자공학부 박사과정 엄소연 수강생은 “논문으로는 이해하기 어려웠던 내용을 실습을 통해 배울 수 있어 의미가 있었다. 특히, 실습 과정에서 얻은 경험과 통찰력은 앞으로 연구와 개발에 큰 도움이 될 것 같다.”라고 소감을 전했다.

수강생들은 질의응답 시간뿐만 아니라 쉬는 시간에도 강사에게 질문을 이어갔다. 미리 관련 논문을 읽고 온 학생들도 있어 PIM 반도체에 대한 열정을 확인할 수 있었다.

2024.07.11 조회수 946 -

김이섭 교수 연구실 박준영 석사졸업생, 국제 반도체 설계 자동화 학회 최우수논문상 수상

우리 대학 전기및전자공학부 김이섭 교수 연구실의 박준영 석사졸업생이 6월 23일 ~ 6월 27일, 미국 샌프란시스코에서 개최된 국제 반도체 설계 자동화 학회 (Design Automation Conference, 이하 DAC) 에서 최우수 논문상(Best Paper Award)을 수상하는 성과를 거두었다. DAC은 1964년에 설립돼 올해 61회째를 맞은, 반도체설계자동화, 인공지능 알고리즘과 칩 설계 등을 포함하는 국제학술대회로서, 제출된 논문 중 상위 20퍼센트 정도만 선정하는, 관련 분야 최고 권위의 학회이다.

수상한 연구는 우리 대학 전기및전자공학부 졸업생 박준영 씨의 석사과정 졸업 논문에 기반한 것으로서, Large Language Model 모델 추론의 문제점이 되는 KV 캐싱의 메모리 전송을 줄이는 알고리즘 근사 기법과 하드웨어 아키텍처를 제안하였으며, 학회 best paper award 선정 위원회로부터 그 우수성을 인정받아 발표논문 337편 중 (제출논문 1,545편) 선정된 4편의 후보 논문중에서 최종 best paper award 수상논문으로 선정되었다.

자세한 내용은 다음과 같다.

– 학 회 명 : 2024 61st IEEE/ACM Design Automation Conference (DAC)

– 개최기간 : 2024년 6월 23일 ~ 27일

– 수 상 명 : Best Paper Award

– 저 자 : 박준영, 강명구, 한윤기, 김양곤, 신재강, 김이섭(지도교수)

– 논 문 명 : Token-Picker : Accelerating Attention in Text Generation with Minimized Memory Transfer via Probability Estimation

2024.07.02 조회수 1007

김이섭 교수 연구실 박준영 석사졸업생, 국제 반도체 설계 자동화 학회 최우수논문상 수상

우리 대학 전기및전자공학부 김이섭 교수 연구실의 박준영 석사졸업생이 6월 23일 ~ 6월 27일, 미국 샌프란시스코에서 개최된 국제 반도체 설계 자동화 학회 (Design Automation Conference, 이하 DAC) 에서 최우수 논문상(Best Paper Award)을 수상하는 성과를 거두었다. DAC은 1964년에 설립돼 올해 61회째를 맞은, 반도체설계자동화, 인공지능 알고리즘과 칩 설계 등을 포함하는 국제학술대회로서, 제출된 논문 중 상위 20퍼센트 정도만 선정하는, 관련 분야 최고 권위의 학회이다.

수상한 연구는 우리 대학 전기및전자공학부 졸업생 박준영 씨의 석사과정 졸업 논문에 기반한 것으로서, Large Language Model 모델 추론의 문제점이 되는 KV 캐싱의 메모리 전송을 줄이는 알고리즘 근사 기법과 하드웨어 아키텍처를 제안하였으며, 학회 best paper award 선정 위원회로부터 그 우수성을 인정받아 발표논문 337편 중 (제출논문 1,545편) 선정된 4편의 후보 논문중에서 최종 best paper award 수상논문으로 선정되었다.

자세한 내용은 다음과 같다.

– 학 회 명 : 2024 61st IEEE/ACM Design Automation Conference (DAC)

– 개최기간 : 2024년 6월 23일 ~ 27일

– 수 상 명 : Best Paper Award

– 저 자 : 박준영, 강명구, 한윤기, 김양곤, 신재강, 김이섭(지도교수)

– 논 문 명 : Token-Picker : Accelerating Attention in Text Generation with Minimized Memory Transfer via Probability Estimation

2024.07.02 조회수 1007 -

K-하이테크 플랫폼 개소식 및 공동세미나 개최

우리 대학이 지난달 27일 경기도 화성시 동탄에 위치한 KAIST-화성 사이언스 허브에서 K-하이테크 플랫폼(센터장 김소영, 과학기술정책대학원 교수) 개소식 및 공동세미나를 개최했다.

K-하이테크 플랫폼은 이차전지, 지능형로봇, 첨단소재, 차세대반도체, 차세대디스플레이, 바이오헬스, 에코업, 신재생에너지, 수소, 양자, 우주, 나노, 기타 신기술 등 국가 경쟁력과 직결되는 핵심 산업의 인재를 양성하는 사업으로 고용노동부가 주관한다. 우리 대학은 지난해 6월 사업 수행기관으로 선정돼 5년간 30억 원의 예산을 지원받아 첨단산업 종사자 · 관심 있는 재직자 · 채용예정자 · 구직자 등을 대상으로 인재를 양성할 예정이다. 특히, 우리 대학 K-하이테크 플랫폼은 세계 수준의 연구 및 교육 성과와 인프라를 바탕으로 인공지능·스마트팩토리·협동로봇·반도체설계 등을 교육한다. 통합형 창의교육 플랫폼을 바탕으로 콘텐츠를 개발해 현장에 적용하고 첨단 분야의 다양한 기업들과 연계해 교육 - 콘텐츠 기획 - 시제품 제작지원 - 기술지원 - 성과전시까지 이어지는 다양한 프로그램을 기획하고 있다.

이날 열린 개소식에는 우리 대학, 화성시, 공동주관기관, 첨단산업기업 등 내·외 관계자 150여 명이 참석했다. 강준혁 전기및전자공학부 학부장, 김소영 K-하이테크 플랫폼 센터장이 환영사하고 박동준 한국산업인력공단 경인지역본부장, 김승희 고용노동부 수원고용센터 소장이 축사했으며, 테이프 커팅 및 현판식이 진행됐다.이어진 KAIST, LG이노텍, 이대서울병원, 한국광융합산업진흥회 공동 주관 세미나에서는 이현주 전기및전자공학부 교수가 '첨단산업과 뇌과학'을 주제로 기조강연하고 유창동 전기및전자공학부 교수는 '생성형 인공지능 기술 동향'을 발표하고 장동의 교수가 좌장을 맡은 좌담회를 열어 신정규 래블업(주) 대표와 심도 있는 토론을 진행했다.

또한, 전상훈 전기및전자공학부 교수가 '반도체산업 기술 동향 및 전망'을 주제로 발표하고 맹원영 내로우채널 대표가 좌장을 맡아 최창주 ㈜제이엠반도체 전무와 김준호 렛유인에듀 대표가 함께 토론을 벌였다.

마지막 세션에서는 전미애 K-하이테크 플랫폼 부센터장이 국가인적자원개발 플랫폼 사업을 소개하고 우송대학교 조남채 교수, 공동주관기관 전담자, 직업훈련전문가, 일반 참여자가 함께하는 자유토론이 진행됐다.김소영 KAIST K-하이테크 플랫폼 센터장은 "인공지능, 반도체, 빅데이터, 바이오헬스 등 첨단 신기술 분야 산업인력 훈련의 중요성이 커지고 있는 시기에 거시적인 변화에 가장 적절히 대응할 수 있는 인력 훈련 체계를 마련하였다는 점에서 국가적으로 매우 뜻깊은 사업"이라고 강조했다. 이어, "과학기술인력 양성의 산실인 KAIST가 첨단 신기술 분야에서 인력 훈련과 현장 중심 산학협력을 고도화하는 본보기를 보여줄 것"이라고 덧붙였다.

2024.07.01 조회수 639

K-하이테크 플랫폼 개소식 및 공동세미나 개최

우리 대학이 지난달 27일 경기도 화성시 동탄에 위치한 KAIST-화성 사이언스 허브에서 K-하이테크 플랫폼(센터장 김소영, 과학기술정책대학원 교수) 개소식 및 공동세미나를 개최했다.

K-하이테크 플랫폼은 이차전지, 지능형로봇, 첨단소재, 차세대반도체, 차세대디스플레이, 바이오헬스, 에코업, 신재생에너지, 수소, 양자, 우주, 나노, 기타 신기술 등 국가 경쟁력과 직결되는 핵심 산업의 인재를 양성하는 사업으로 고용노동부가 주관한다. 우리 대학은 지난해 6월 사업 수행기관으로 선정돼 5년간 30억 원의 예산을 지원받아 첨단산업 종사자 · 관심 있는 재직자 · 채용예정자 · 구직자 등을 대상으로 인재를 양성할 예정이다. 특히, 우리 대학 K-하이테크 플랫폼은 세계 수준의 연구 및 교육 성과와 인프라를 바탕으로 인공지능·스마트팩토리·협동로봇·반도체설계 등을 교육한다. 통합형 창의교육 플랫폼을 바탕으로 콘텐츠를 개발해 현장에 적용하고 첨단 분야의 다양한 기업들과 연계해 교육 - 콘텐츠 기획 - 시제품 제작지원 - 기술지원 - 성과전시까지 이어지는 다양한 프로그램을 기획하고 있다.

이날 열린 개소식에는 우리 대학, 화성시, 공동주관기관, 첨단산업기업 등 내·외 관계자 150여 명이 참석했다. 강준혁 전기및전자공학부 학부장, 김소영 K-하이테크 플랫폼 센터장이 환영사하고 박동준 한국산업인력공단 경인지역본부장, 김승희 고용노동부 수원고용센터 소장이 축사했으며, 테이프 커팅 및 현판식이 진행됐다.이어진 KAIST, LG이노텍, 이대서울병원, 한국광융합산업진흥회 공동 주관 세미나에서는 이현주 전기및전자공학부 교수가 '첨단산업과 뇌과학'을 주제로 기조강연하고 유창동 전기및전자공학부 교수는 '생성형 인공지능 기술 동향'을 발표하고 장동의 교수가 좌장을 맡은 좌담회를 열어 신정규 래블업(주) 대표와 심도 있는 토론을 진행했다.

또한, 전상훈 전기및전자공학부 교수가 '반도체산업 기술 동향 및 전망'을 주제로 발표하고 맹원영 내로우채널 대표가 좌장을 맡아 최창주 ㈜제이엠반도체 전무와 김준호 렛유인에듀 대표가 함께 토론을 벌였다.

마지막 세션에서는 전미애 K-하이테크 플랫폼 부센터장이 국가인적자원개발 플랫폼 사업을 소개하고 우송대학교 조남채 교수, 공동주관기관 전담자, 직업훈련전문가, 일반 참여자가 함께하는 자유토론이 진행됐다.김소영 KAIST K-하이테크 플랫폼 센터장은 "인공지능, 반도체, 빅데이터, 바이오헬스 등 첨단 신기술 분야 산업인력 훈련의 중요성이 커지고 있는 시기에 거시적인 변화에 가장 적절히 대응할 수 있는 인력 훈련 체계를 마련하였다는 점에서 국가적으로 매우 뜻깊은 사업"이라고 강조했다. 이어, "과학기술인력 양성의 산실인 KAIST가 첨단 신기술 분야에서 인력 훈련과 현장 중심 산학협력을 고도화하는 본보기를 보여줄 것"이라고 덧붙였다.

2024.07.01 조회수 639 -

애물단지 열을 컴퓨팅에 활용한다

기존의 반도체 소자에서 열 발생은 피할 수 없는데, 이는 에너지 소모량을 증가시키고, 반도체의 정상적인 동작을 방해하기 때문에 문제가 되며, 이에 열 발생을 최소화하는 것이 기존 반도체 기술의 관건이었다. KAIST 연구진이 이렇게 애물단지로 여겨지던 열을 오히려 컴퓨팅에 활용하는 방법을 고안하여 화제다.

우리 대학 신소재공학과 김경민 교수 연구팀이 산화물 반도체의 열-전기 상호작용에 기반하는 열 컴퓨팅(Thermal computing) 기술 개발에 성공했다고 25일 밝혔다.

연구팀은 전기-열 상호작용이 강한 모트 전이 (Mott transition) 반도체*를 활용했으며, 이 반도체 소자에 열 저장 및 열전달 기능을 최적화해 열을 이용하는 컴퓨팅을 구현했다. 이렇게 개발된 열 컴퓨팅 기술은 기존의 CPU, GPU와 같은 디지털 프로세서보다 1,000,000(백만)분의 1 수준의 에너지만으로 경로 찾기 등과 같은 복잡한 최적화 문제를 풀 수 있었다.

*모트 전이 반도체: 온도에 따라 전기적 특성이 부도체에서 도체로 변하는 전기-열 상호작용이 강한 반도체 소자

본 연구에서는 낮은 열전도도와 높은 비열을 가지고 있는 폴리이미드* 기판 상에 모트 전이 반도체 소자를 제작하여, 모트 전이 반도체 소자에서 발생한 열이 폴리이미드 기판에 저장이 될 수 있도록 하였다. 이렇게 저장된 열은 일정 시간 동안 유지되며 시간적 정보 역할을 하였다. 또한, 이 열은 공간적으로도 이웃 소자로 전파되게 되는데, 이는 공간적 정보 역할을 하였다. 이처럼 열 정보를 시공간적으로 활용할 수 있었으며, 이를 활용하여 컴퓨팅을 수행할 수 있었다.

*폴리이미드: 우수한 기계적 강도, 유연성, 내열성을 가진 폴리머 소재. 디스플레이, 태양전지, 메모리 등에 다양하게 활용됨

김경민 교수는 “단순히 전기 신호만 사용하던 컴퓨팅 기술은 이제 한계에 이르렀으며, 열은 저장할 수 있고, 전달할 수 있는 특성이 있어 이를 잘 활용할 수만 있다면 컴퓨팅에서 매우 유용하게 쓰일 수 있다”며 “이번 연구의 의미는 기존에는 버려지던 열을 컴퓨팅에 활용할 수 있다는 개념을 최초로 제안한 데 있다”고 연구의 의미에 대해서 말했다.

또한 “열 컴퓨팅 기술을 활용하면 뉴런과 같은 신경계의 복잡한 신호도 매우 간단히 구현할 수 있으며, 또한 고차원의 최적화 문제를 기존의 반도체 기술을 바탕으로 효과적으로 해결할 수 있어 양자 컴퓨팅의 현실적인 대안이 될 수 있다”고 기술의 장점을 설명했다. 그리고“이번 연구는 미국의 샌디아 국립 연구소(Sandia National Laboratory)와의 공동 연구로 검증된 결과”라는 점을 강조했다.

이번 연구는 신소재공학과 김광민 박사과정, 인재현 박사, 이영현 박사과정 학생이 공동 제1 저자로 참여했으며 재료 분야 최고 권위의 국제 학술지 `네이처 머티리얼즈(Nature Materials, Impact factor: 41.2)'에 6월 18일 字에 게재됐다.

(논문명 : Mott Neurons with Dual Thermal Dynamics for Spatiotemporal Computing).

한편 이번 연구는 한국연구재단, 나노종합기술원, KAIST의 지원을 받아 수행됐다.

2024.06.25 조회수 1309

애물단지 열을 컴퓨팅에 활용한다

기존의 반도체 소자에서 열 발생은 피할 수 없는데, 이는 에너지 소모량을 증가시키고, 반도체의 정상적인 동작을 방해하기 때문에 문제가 되며, 이에 열 발생을 최소화하는 것이 기존 반도체 기술의 관건이었다. KAIST 연구진이 이렇게 애물단지로 여겨지던 열을 오히려 컴퓨팅에 활용하는 방법을 고안하여 화제다.

우리 대학 신소재공학과 김경민 교수 연구팀이 산화물 반도체의 열-전기 상호작용에 기반하는 열 컴퓨팅(Thermal computing) 기술 개발에 성공했다고 25일 밝혔다.

연구팀은 전기-열 상호작용이 강한 모트 전이 (Mott transition) 반도체*를 활용했으며, 이 반도체 소자에 열 저장 및 열전달 기능을 최적화해 열을 이용하는 컴퓨팅을 구현했다. 이렇게 개발된 열 컴퓨팅 기술은 기존의 CPU, GPU와 같은 디지털 프로세서보다 1,000,000(백만)분의 1 수준의 에너지만으로 경로 찾기 등과 같은 복잡한 최적화 문제를 풀 수 있었다.

*모트 전이 반도체: 온도에 따라 전기적 특성이 부도체에서 도체로 변하는 전기-열 상호작용이 강한 반도체 소자

본 연구에서는 낮은 열전도도와 높은 비열을 가지고 있는 폴리이미드* 기판 상에 모트 전이 반도체 소자를 제작하여, 모트 전이 반도체 소자에서 발생한 열이 폴리이미드 기판에 저장이 될 수 있도록 하였다. 이렇게 저장된 열은 일정 시간 동안 유지되며 시간적 정보 역할을 하였다. 또한, 이 열은 공간적으로도 이웃 소자로 전파되게 되는데, 이는 공간적 정보 역할을 하였다. 이처럼 열 정보를 시공간적으로 활용할 수 있었으며, 이를 활용하여 컴퓨팅을 수행할 수 있었다.

*폴리이미드: 우수한 기계적 강도, 유연성, 내열성을 가진 폴리머 소재. 디스플레이, 태양전지, 메모리 등에 다양하게 활용됨

김경민 교수는 “단순히 전기 신호만 사용하던 컴퓨팅 기술은 이제 한계에 이르렀으며, 열은 저장할 수 있고, 전달할 수 있는 특성이 있어 이를 잘 활용할 수만 있다면 컴퓨팅에서 매우 유용하게 쓰일 수 있다”며 “이번 연구의 의미는 기존에는 버려지던 열을 컴퓨팅에 활용할 수 있다는 개념을 최초로 제안한 데 있다”고 연구의 의미에 대해서 말했다.

또한 “열 컴퓨팅 기술을 활용하면 뉴런과 같은 신경계의 복잡한 신호도 매우 간단히 구현할 수 있으며, 또한 고차원의 최적화 문제를 기존의 반도체 기술을 바탕으로 효과적으로 해결할 수 있어 양자 컴퓨팅의 현실적인 대안이 될 수 있다”고 기술의 장점을 설명했다. 그리고“이번 연구는 미국의 샌디아 국립 연구소(Sandia National Laboratory)와의 공동 연구로 검증된 결과”라는 점을 강조했다.

이번 연구는 신소재공학과 김광민 박사과정, 인재현 박사, 이영현 박사과정 학생이 공동 제1 저자로 참여했으며 재료 분야 최고 권위의 국제 학술지 `네이처 머티리얼즈(Nature Materials, Impact factor: 41.2)'에 6월 18일 字에 게재됐다.

(논문명 : Mott Neurons with Dual Thermal Dynamics for Spatiotemporal Computing).

한편 이번 연구는 한국연구재단, 나노종합기술원, KAIST의 지원을 받아 수행됐다.

2024.06.25 조회수 1309 -

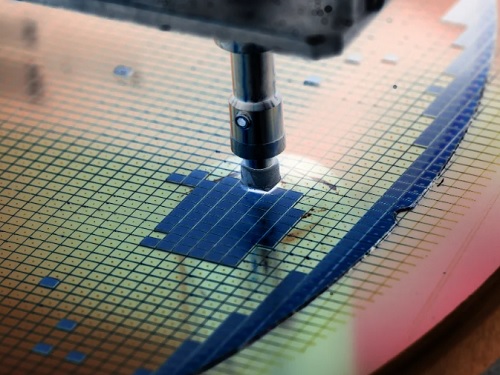

차세대 이차원 반도체 핵심 기술 개발

물질 증착, 패터닝, 식각 등 복잡한 과정들이 필요했던 기존 반도체 공정과는 달리, 원하는 영역에서만 선택적으로 물질을 바로 증착하는 기술은 공정을 획기적으로 줄일 수 있는 차세대 기술로 크게 주목받고 있다. 특히, 현재의 실리콘을 대체할 차세대 이차원 반도체에서 이런 선택적 증착 기술 개발이 핵심 요소기술로 중요성이 더욱 커지고 있다.

우리 대학 신소재공학과 강기범 교수 연구팀과 고려대학교 김용주 교수 연구팀이 이차원 반도체의 수평 성장 성질을 이용해 쉽고 간편한 산화물, 금속 등의 10나노미터 이하 미세 패터닝 기술을 공동 개발했다고 28일 밝혔다.

강 교수 연구팀은 차세대 반도체 물질로 주목받는 이차원 전이금속 ‘칼코겐’ 물질의 독특한 결정학적 특징을 패터닝 기술에 접목했다. 일반적인 물질과는 달리 이차원 물질은 성장 시 수평 방향으로만 자랄 수 있기에 서로 다른 이차원 물질을 반복적으로 성장해 10나노미터 이하 수준의 이차원 반도체 선형 패턴을 제작할 수 있다.

이러한 선형 패턴에 다양한 물질(산화물, 금속, 상변화 물질)을 성장할 때 한 영역 위에서만 선택적으로 증착되는 현상을 최초로 발견했다. 해당 기술을 통해 타깃 물질 패턴 크기의 축소와 이차원 반도체의 소자 제작 공정 효율성 증대 등을 기대할 수 있다.

일반적으로 선형 패턴의 크기는 이차원 물질 합성에 사용되는 기체 상태의 분자들의 유입 시간으로 결정된다. 해당 연구에서는 약 1초당 1나노미터의 패턴 크기를 형성할 수 있기에 기존 광 기반 패터닝 기술에 비해 효과적으로 크기를 줄일 수 있다.

연구팀이 개발한 선택 증착 기술은 선폭 10나노미터 수준의 좁은 패턴에서도 원하는 물질이 한 영역 위에서만 선택적으로 증착됐으며, 기존 기술과는 달리 두께 20나노미터 이상에서도 선택적 증착이 가능했다.

연구팀이 개발한 기술은 다양한 물질들에서 적용할 수 있다. 반도체 산업에서 소자 제작에 필수적으로 활용되는 고유전율 절연체(산화 알루미늄, 산화 하프늄)와 전극 금속(루테늄) 등의 선택적 증착을 확인했다. 이러한 뛰어난 물질 확장성은 연구팀이 제시한 새로운 선택 증착 메커니즘에 의해 가능한 것으로 알려졌으며, 추후 더 넓은 응용 기술 개발에 활용할 것으로 기대된다.

연구팀의 기술은 차세대 물질인 이차원 반도체 기반에서 적용되기에 이차원 반도체에 효과적으로 게이트 절연체 및 전극의 형성을 도울 것으로 기대된다. 이는 향후 이차원 반도체가 실리콘을 대체할 때 핵심적인 요소기술로 작용할 것이며, 한국에서 가장 중요한 연구 분야인 반도체 시장에서 활발히 응용될 수 있다.

제1 저자인 박정원 연구원은 "새로운 원리의 선택 증착 기술이자 다양한 물질을 10나노미터 이하의 선폭으로 패터닝할 수 있는 차세대 기술을 개발했다ˮ 라며 "특히 템플릿으로 사용되는 이차원 반도체에 선택 증착을 통해 게이트 산화물과 전극 등으로 직접 이용하면 이 기술의 기대 효과는 더욱 커진다ˮ 라고 말했다.

신소재공학과 박정원 석박사통합과정이 제1 저자로 참여한 이번 연구는 국제 학술지 `네이처 커뮤니케이션즈(Nature Communications)' 3월 15권에 3월 8일 자 출판됐다. (논문명 : Area-selective atomic layer deposition on 2D monolayer lateral superlattices).

한편 이번 연구는 한국연구재단의 지원을 받아 수행됐다.

2024.03.28 조회수 1930

차세대 이차원 반도체 핵심 기술 개발

물질 증착, 패터닝, 식각 등 복잡한 과정들이 필요했던 기존 반도체 공정과는 달리, 원하는 영역에서만 선택적으로 물질을 바로 증착하는 기술은 공정을 획기적으로 줄일 수 있는 차세대 기술로 크게 주목받고 있다. 특히, 현재의 실리콘을 대체할 차세대 이차원 반도체에서 이런 선택적 증착 기술 개발이 핵심 요소기술로 중요성이 더욱 커지고 있다.

우리 대학 신소재공학과 강기범 교수 연구팀과 고려대학교 김용주 교수 연구팀이 이차원 반도체의 수평 성장 성질을 이용해 쉽고 간편한 산화물, 금속 등의 10나노미터 이하 미세 패터닝 기술을 공동 개발했다고 28일 밝혔다.

강 교수 연구팀은 차세대 반도체 물질로 주목받는 이차원 전이금속 ‘칼코겐’ 물질의 독특한 결정학적 특징을 패터닝 기술에 접목했다. 일반적인 물질과는 달리 이차원 물질은 성장 시 수평 방향으로만 자랄 수 있기에 서로 다른 이차원 물질을 반복적으로 성장해 10나노미터 이하 수준의 이차원 반도체 선형 패턴을 제작할 수 있다.

이러한 선형 패턴에 다양한 물질(산화물, 금속, 상변화 물질)을 성장할 때 한 영역 위에서만 선택적으로 증착되는 현상을 최초로 발견했다. 해당 기술을 통해 타깃 물질 패턴 크기의 축소와 이차원 반도체의 소자 제작 공정 효율성 증대 등을 기대할 수 있다.

일반적으로 선형 패턴의 크기는 이차원 물질 합성에 사용되는 기체 상태의 분자들의 유입 시간으로 결정된다. 해당 연구에서는 약 1초당 1나노미터의 패턴 크기를 형성할 수 있기에 기존 광 기반 패터닝 기술에 비해 효과적으로 크기를 줄일 수 있다.

연구팀이 개발한 선택 증착 기술은 선폭 10나노미터 수준의 좁은 패턴에서도 원하는 물질이 한 영역 위에서만 선택적으로 증착됐으며, 기존 기술과는 달리 두께 20나노미터 이상에서도 선택적 증착이 가능했다.

연구팀이 개발한 기술은 다양한 물질들에서 적용할 수 있다. 반도체 산업에서 소자 제작에 필수적으로 활용되는 고유전율 절연체(산화 알루미늄, 산화 하프늄)와 전극 금속(루테늄) 등의 선택적 증착을 확인했다. 이러한 뛰어난 물질 확장성은 연구팀이 제시한 새로운 선택 증착 메커니즘에 의해 가능한 것으로 알려졌으며, 추후 더 넓은 응용 기술 개발에 활용할 것으로 기대된다.

연구팀의 기술은 차세대 물질인 이차원 반도체 기반에서 적용되기에 이차원 반도체에 효과적으로 게이트 절연체 및 전극의 형성을 도울 것으로 기대된다. 이는 향후 이차원 반도체가 실리콘을 대체할 때 핵심적인 요소기술로 작용할 것이며, 한국에서 가장 중요한 연구 분야인 반도체 시장에서 활발히 응용될 수 있다.

제1 저자인 박정원 연구원은 "새로운 원리의 선택 증착 기술이자 다양한 물질을 10나노미터 이하의 선폭으로 패터닝할 수 있는 차세대 기술을 개발했다ˮ 라며 "특히 템플릿으로 사용되는 이차원 반도체에 선택 증착을 통해 게이트 산화물과 전극 등으로 직접 이용하면 이 기술의 기대 효과는 더욱 커진다ˮ 라고 말했다.

신소재공학과 박정원 석박사통합과정이 제1 저자로 참여한 이번 연구는 국제 학술지 `네이처 커뮤니케이션즈(Nature Communications)' 3월 15권에 3월 8일 자 출판됐다. (논문명 : Area-selective atomic layer deposition on 2D monolayer lateral superlattices).

한편 이번 연구는 한국연구재단의 지원을 받아 수행됐다.

2024.03.28 조회수 1930 -

화학물질 없이 식각하는 반도체 기술 최초 개발

차세대 반도체 메모리의 소재로 주목을 받고 있는 강유전체는 차세대 메모리 소자 혹은 작은 물리적 변화를 감지하는 센서로 활용되는 등 그 중요성이 커지고 있다. 이에 반도체의 핵심 소자가 되는 강유전체를 화학물질없이 식각할 수 있는 연구를 성공해 화제다.

우리 대학 신소재공학과 홍승범 교수가 제네바 대학교와 국제공동연구를 통해 강유전체 표면의 비대칭 마멸* 현상을 세계 최초로 관찰 및 규명했고, 이를 활용해 혁신적인 나노 패터닝 기술**을 개발했다고 26일 밝혔다.

*마멸: 물체 표면의 재료가 점진적으로 손실 또는 제거되는 현상

**나노 패터닝 기술: 나노스케일로 소재의 표면에 정밀한 패턴을 생성하여 다양한 첨단 기술 분야에서 제품 성능을 향상시키는데 사용되는 기술

연구팀은 강유전체 소재의 표면 특성에 관한 연구에 집중했다. 이들은 원자간력 현미경(Atomic Force Microscopy)을 활용해 다양한 강유전체의 트라이볼로지(Tribology, 마찰 및 마모) 현상을 관찰했고, 강유전체의 전기적인 분극* 방향에 따라 마찰되거나 마모되는 특성이 다르다는 것을 세계 최초로 발견했다. (그림 1) 아울러, 이러한 분극 방향에 따라 달라지는 트라이볼로지의 원인으로 변전 효과(Flexoelectric effect)*에 주목했다.

*전기적 분극(electric dipole): 자석의 북극과 남극처럼 전기적으로 양극과 음극이 있는 것을 의미함

*변전 효과: 물질이 휘어졌을 때 분극이 발생하는 현상이지만, 거시 규모에서 물질을 구부렸을 때 유도되는 분극의 크기가 매우 작아 그동안 큰 주목을 받지 못했다. 그러나 2010년대 들어서 물질이 나노스케일로 미세화될 경우, 매우 큰 변전 효과가 발생할 수 있다는 연구 결과가 나오면서 많은 연구자의 주목을 받기 시작했다.

연구진은 강유전체의 트라이볼로지 특성이 나노 단위에서 강한 응력이 가해질 때 발생하는 변전 효과로 인해 강유전체 내부의 분극 방향에 따른 상호작용으로 트라이볼로지 특성이 바뀌게 된다는 것을 발견했다. 또한 이러한 새로운 강유전체 트라이볼로지 현상을 소재의 나노 패터닝에 응용했다.

이러한 패터닝 방식은 기존의 반도체 패터닝 방식과는 다르게 화학 물질 및 고비용의 리소그래피 장비가 필요하지 않고, 기존 공정 대비 매우 빠르게 나노 구조를 제작할 수 있는 장점이 있다.

이번 연구의 제1 저자인 신소재공학과 졸업생 조성우 박사는 “이번 연구는 세계 최초로 강유전체 비대칭 트라이볼로지를 관찰하고 규명한 데 의의가 있고, 이러한 분극에 민감한 트라이볼로지 비대칭성이 다양한 화학적 구성 및 결정 구조를 가진 강유전체에서 널리 적용될 수 있어 많은 후속 연구를 기대할 수 있다”고 밝혔다.

공동교신저자로 본 연구를 공동 지도한 제네바 대학교 파루치(Paruch) 교수는 “변전 효과를 통해 강유전체의 도메인이 분극 방향에 따라 서로 다른 표면 특성을 나타내는 것을 활용함으로써, 다양하고 유용한 기술들을 개발할 수 있을 것이다”며 이번 연구가 앞으로 뻗어나갈 분야에 대한 강한 자신감을 피력했다.

연구를 이끈 홍승범 교수는 “이번 연구에서 개발된 패터닝 기술은 기존 반도체 공정에서 쓰이는 패터닝 공정과 달리 화학 물질을 사용하지 않고, 매우 낮은 비용으로 대면적 나노 구조를 만들 수 있어 산업적으로 활용될 수 있는 잠재력을 가지고 있다”고 전망했다.

한편, 이번 연구는 한국연구재단(2020R1A2C2012078, NRF-2022K1A4A7A04095892, RS-2023-00247245), KAIST 글로벌특이점 사업의 지원 및 스위스, 스페인 연구진과의 국제공동연구를 통해 수행됐으며, 국제 학술지 ‘네이처 커뮤니케이션즈(Nature Communications)’에 1월 9일 자 출판됐다. (논문 제목: Switchable tribology of ferroelectrics)

2024.03.26 조회수 2326

화학물질 없이 식각하는 반도체 기술 최초 개발

차세대 반도체 메모리의 소재로 주목을 받고 있는 강유전체는 차세대 메모리 소자 혹은 작은 물리적 변화를 감지하는 센서로 활용되는 등 그 중요성이 커지고 있다. 이에 반도체의 핵심 소자가 되는 강유전체를 화학물질없이 식각할 수 있는 연구를 성공해 화제다.

우리 대학 신소재공학과 홍승범 교수가 제네바 대학교와 국제공동연구를 통해 강유전체 표면의 비대칭 마멸* 현상을 세계 최초로 관찰 및 규명했고, 이를 활용해 혁신적인 나노 패터닝 기술**을 개발했다고 26일 밝혔다.

*마멸: 물체 표면의 재료가 점진적으로 손실 또는 제거되는 현상

**나노 패터닝 기술: 나노스케일로 소재의 표면에 정밀한 패턴을 생성하여 다양한 첨단 기술 분야에서 제품 성능을 향상시키는데 사용되는 기술

연구팀은 강유전체 소재의 표면 특성에 관한 연구에 집중했다. 이들은 원자간력 현미경(Atomic Force Microscopy)을 활용해 다양한 강유전체의 트라이볼로지(Tribology, 마찰 및 마모) 현상을 관찰했고, 강유전체의 전기적인 분극* 방향에 따라 마찰되거나 마모되는 특성이 다르다는 것을 세계 최초로 발견했다. (그림 1) 아울러, 이러한 분극 방향에 따라 달라지는 트라이볼로지의 원인으로 변전 효과(Flexoelectric effect)*에 주목했다.

*전기적 분극(electric dipole): 자석의 북극과 남극처럼 전기적으로 양극과 음극이 있는 것을 의미함

*변전 효과: 물질이 휘어졌을 때 분극이 발생하는 현상이지만, 거시 규모에서 물질을 구부렸을 때 유도되는 분극의 크기가 매우 작아 그동안 큰 주목을 받지 못했다. 그러나 2010년대 들어서 물질이 나노스케일로 미세화될 경우, 매우 큰 변전 효과가 발생할 수 있다는 연구 결과가 나오면서 많은 연구자의 주목을 받기 시작했다.

연구진은 강유전체의 트라이볼로지 특성이 나노 단위에서 강한 응력이 가해질 때 발생하는 변전 효과로 인해 강유전체 내부의 분극 방향에 따른 상호작용으로 트라이볼로지 특성이 바뀌게 된다는 것을 발견했다. 또한 이러한 새로운 강유전체 트라이볼로지 현상을 소재의 나노 패터닝에 응용했다.

이러한 패터닝 방식은 기존의 반도체 패터닝 방식과는 다르게 화학 물질 및 고비용의 리소그래피 장비가 필요하지 않고, 기존 공정 대비 매우 빠르게 나노 구조를 제작할 수 있는 장점이 있다.

이번 연구의 제1 저자인 신소재공학과 졸업생 조성우 박사는 “이번 연구는 세계 최초로 강유전체 비대칭 트라이볼로지를 관찰하고 규명한 데 의의가 있고, 이러한 분극에 민감한 트라이볼로지 비대칭성이 다양한 화학적 구성 및 결정 구조를 가진 강유전체에서 널리 적용될 수 있어 많은 후속 연구를 기대할 수 있다”고 밝혔다.

공동교신저자로 본 연구를 공동 지도한 제네바 대학교 파루치(Paruch) 교수는 “변전 효과를 통해 강유전체의 도메인이 분극 방향에 따라 서로 다른 표면 특성을 나타내는 것을 활용함으로써, 다양하고 유용한 기술들을 개발할 수 있을 것이다”며 이번 연구가 앞으로 뻗어나갈 분야에 대한 강한 자신감을 피력했다.

연구를 이끈 홍승범 교수는 “이번 연구에서 개발된 패터닝 기술은 기존 반도체 공정에서 쓰이는 패터닝 공정과 달리 화학 물질을 사용하지 않고, 매우 낮은 비용으로 대면적 나노 구조를 만들 수 있어 산업적으로 활용될 수 있는 잠재력을 가지고 있다”고 전망했다.

한편, 이번 연구는 한국연구재단(2020R1A2C2012078, NRF-2022K1A4A7A04095892, RS-2023-00247245), KAIST 글로벌특이점 사업의 지원 및 스위스, 스페인 연구진과의 국제공동연구를 통해 수행됐으며, 국제 학술지 ‘네이처 커뮤니케이션즈(Nature Communications)’에 1월 9일 자 출판됐다. (논문 제목: Switchable tribology of ferroelectrics)

2024.03.26 조회수 2326 -

극저온일수록 강력한 초고속 반도체 소자 개발

KAIST 연구진이 초고속 구동이 가능하고 온도가 낮아질수록 성능이 더욱 향상되어 고주파수 대역 및 극저온에서의 활용 가능성이 기대되는 고성능 2차원 반도체 소자 개발에 성공하였다.

전기및전자공학부 이가영 교수 연구팀이 실리콘의 전자 이동도와 포화 속도*를 2배 이상 뛰어넘는 2차원 나노 반도체 인듐 셀레나이드(InSe)** 기반 고이동도, 초고속 소자를 개발했다고 20일 밝혔다.

*포화 속도(Saturation velocity): 반도체 물질 내에서 전자나 정공이 움직일 수 있는 최대 속도를 가리킴. 포화 속도는 포화 전류량 및 차단 주파수(Cutoff frequency) 등을 결정하며 반도체의 전기적 특성을 평가할 수 있는 핵심 지표 중 하나임.

**인듐 셀레나이드(InSe): 인듐과 셀레늄으로 이루어진 무기 화합물로 2차원 층간 반데르발스 결합을 이루고 있음

연구진은 고이동도 인듐 셀레나이드에서의 2.0×107 cm/s를 초과하는 우수한 상온 전자 포화 속도 값을 달성하였는데, 이는 실리콘과 다른 유효한 밴드갭을 지니는 타 2차원 반도체들의 값보다 월등히 우수한 수치이다. 특히 80 K으로 냉각시 InSe의 전자 포화 속도는 최대 3.9×107 cm/s로 상온 대비 50% 이상 향상되는데, 이는 전자 포화 속도가 약 20% 정도만 상승하는 실리콘 그리고 냉각하여도 포화 속도에 거의 변화가 없는 그래핀 대비 주목할만하다. 인듐 셀레나이드의 전자 포화 속도를 체계적으로 분석하여 보고한 것은 이번이 처음이며, 연구진은 전자 포화 속도 양상의 결정 기제 또한 규명하였다.

*이종접합: 서로 다른 결정 반도체의 2개의 층 또는 영역 사이의 접점

이번 연구를 주도한 석용욱 학생은 “고성능 소자 개발을 통해 2차원 반도체 InSe의 높은 전자 이동도와 포화 속도를 확인할 수 있었다”며 “실제 극저온 및 고주파수 구동이 필요한 응용 기기에의 적용 연구가 필요하다”라고 덧붙였다.

이가영 교수는 “고주파수 전자 시스템 구현에는 높은 포화 속도가 요구되는데 이번에 개발한 고성능 전자 소자는 초고속 구동이 가능하여 5G 대역을 넘어 6G 주파수 대역에서의 동작이 가능할 것으로 예측된다”며 “저온으로 갈수록 소자의 성능이 더욱 향상되어 퀀텀 컴퓨터의 양자 제어 IC(Integrated circuit)와 같이 극저온 고주파수 구동 환경에 적합하다.”라고 말했다.

KAIST 전기및전자공학부 석용욱 박사과정 학생이 제1저자로 참여한 이번 연구는 나노과학 분야 저명 국제 학술지 `ACS Nano'에 2024년 3월 19일 정식 출판됐으며 동시에 저널 표지 논문으로 채택됐다. (논문명 : High-Field Electron Transport and High Saturation Velocity in Multilayer Indium Selenide Transistors)

한편 이번 연구는 한국연구재단의 신진연구자지원사업, 기초연구사업 및 BK21, KAIST의 C2(Creative & Challenging) 프로젝트, LX 세미콘-KAIST 미래기술센터, 그리고 포스코청암재단의 지원을 받아 수행됐다.

붙임 : 연구개요, 그림 설명, 교수 이력

2024.03.20 조회수 2348

극저온일수록 강력한 초고속 반도체 소자 개발

KAIST 연구진이 초고속 구동이 가능하고 온도가 낮아질수록 성능이 더욱 향상되어 고주파수 대역 및 극저온에서의 활용 가능성이 기대되는 고성능 2차원 반도체 소자 개발에 성공하였다.

전기및전자공학부 이가영 교수 연구팀이 실리콘의 전자 이동도와 포화 속도*를 2배 이상 뛰어넘는 2차원 나노 반도체 인듐 셀레나이드(InSe)** 기반 고이동도, 초고속 소자를 개발했다고 20일 밝혔다.

*포화 속도(Saturation velocity): 반도체 물질 내에서 전자나 정공이 움직일 수 있는 최대 속도를 가리킴. 포화 속도는 포화 전류량 및 차단 주파수(Cutoff frequency) 등을 결정하며 반도체의 전기적 특성을 평가할 수 있는 핵심 지표 중 하나임.

**인듐 셀레나이드(InSe): 인듐과 셀레늄으로 이루어진 무기 화합물로 2차원 층간 반데르발스 결합을 이루고 있음

연구진은 고이동도 인듐 셀레나이드에서의 2.0×107 cm/s를 초과하는 우수한 상온 전자 포화 속도 값을 달성하였는데, 이는 실리콘과 다른 유효한 밴드갭을 지니는 타 2차원 반도체들의 값보다 월등히 우수한 수치이다. 특히 80 K으로 냉각시 InSe의 전자 포화 속도는 최대 3.9×107 cm/s로 상온 대비 50% 이상 향상되는데, 이는 전자 포화 속도가 약 20% 정도만 상승하는 실리콘 그리고 냉각하여도 포화 속도에 거의 변화가 없는 그래핀 대비 주목할만하다. 인듐 셀레나이드의 전자 포화 속도를 체계적으로 분석하여 보고한 것은 이번이 처음이며, 연구진은 전자 포화 속도 양상의 결정 기제 또한 규명하였다.

*이종접합: 서로 다른 결정 반도체의 2개의 층 또는 영역 사이의 접점

이번 연구를 주도한 석용욱 학생은 “고성능 소자 개발을 통해 2차원 반도체 InSe의 높은 전자 이동도와 포화 속도를 확인할 수 있었다”며 “실제 극저온 및 고주파수 구동이 필요한 응용 기기에의 적용 연구가 필요하다”라고 덧붙였다.

이가영 교수는 “고주파수 전자 시스템 구현에는 높은 포화 속도가 요구되는데 이번에 개발한 고성능 전자 소자는 초고속 구동이 가능하여 5G 대역을 넘어 6G 주파수 대역에서의 동작이 가능할 것으로 예측된다”며 “저온으로 갈수록 소자의 성능이 더욱 향상되어 퀀텀 컴퓨터의 양자 제어 IC(Integrated circuit)와 같이 극저온 고주파수 구동 환경에 적합하다.”라고 말했다.

KAIST 전기및전자공학부 석용욱 박사과정 학생이 제1저자로 참여한 이번 연구는 나노과학 분야 저명 국제 학술지 `ACS Nano'에 2024년 3월 19일 정식 출판됐으며 동시에 저널 표지 논문으로 채택됐다. (논문명 : High-Field Electron Transport and High Saturation Velocity in Multilayer Indium Selenide Transistors)

한편 이번 연구는 한국연구재단의 신진연구자지원사업, 기초연구사업 및 BK21, KAIST의 C2(Creative & Challenging) 프로젝트, LX 세미콘-KAIST 미래기술센터, 그리고 포스코청암재단의 지원을 받아 수행됐다.

붙임 : 연구개요, 그림 설명, 교수 이력

2024.03.20 조회수 2348 -

해킹 공격 막는 암호 반도체 최초 개발

사물인터넷(IoT), 자율 주행 등 5G/6G 시대 소자 또는 기기 간의 상호 정보 교환이 급증함에 따라 해킹 공격이 고도화되고 있다. 이에 따라, 기기에서 데이터를 안전하게 전송하기 위해서는 보안 기능 강화가 필수적이다.

우리 대학 전기및전자공학부 최양규 교수와 류승탁 교수 공동연구팀이 ‘해킹 막는 세계 최초 보안용 암호 반도체’를 개발하는 데 성공했다고 29일 밝혔다.

연구팀은 100% 실리콘 호환 공정으로 제작된 핀펫(FinFET) 기반 보안용 암호반도체 크립토그래픽 트랜지스터(cryptographic transistor, 이하 크립토리스터(cryptoristor))를 세계 최초로 개발했다. 이는 트랜지스터 하나로 이루어진 독창적 구조를 갖고 있을 뿐만 아니라, 동작 방식 또한 독특해 유일무이한 특성을 구비한 난수발생기다.

인공지능 등의 모든 보안 환경에서 가장 중요한 요소는 난수발생기이다. 가장 널리 사용되는 보안 칩인 ‘고급 암호화 표준(advanced encryption standard, AES)’에서 난수발생기는 핵심 요소로, AES 보안 칩 전체 면적의 약 75%, 에너지 소모의 85% 이상을 차지한다. 따라서, 모바일 혹은 사물인터넷(IoT)에 탑재가 가능한 저전력/초소형 난수발생기 개발이 시급하다.

기존의 난수발생기는 전력 소모가 매우 크고 실리콘 CMOS 공정과의 호환성이 떨어진다는 단점이 있고, 회로 기반의 난수발생기들은 점유 면적이 매우 크다는 단점이 있다.

연구팀은 기존 세계 최고 수준 연구 대비 전력 소모와 점유 면적 모두 수천 배 이상 작은 암호 반도체인 단일 소자 기반의 크립토리스터(cryptoristor)를 개발했다. 절연층이 실리콘 하부에 형성되어 있는 실리콘 온 인슐레이터(Silicon-on-Insulator, SOI) 기판 위에 제작된 핀펫(FinFET)이 가지는 내재적인 전위 불안정성을 이용해 무작위적으로 0과 1을 예측 불가능하게 내보내는 난수발생기를 개발했다.

다시 설명하면, 보통 모바일 기기 등에서 정보를 교환할 때 데이터를 암호화하는 알고리즘에는 해커가 암호화한 알고리즘을 예측할 수 없도록 하는 것이 중요하다. 이에 무작위의 0과 1이 난수이며 0과 1의 배열이 매번 다른 결과가 나오게 하여 예측 불가능성을 가지도록 함으로써 공격자가 예측하지 못하도록 차단하는 방식이다.

특히, 크립토리스터 기반 난수발생기 연구는 국제적으로도 구현한 사례가 없는 세계 최초의 연구이면서, 기존 논리 연산용 또는 메모리용 소자와 동일한 구조의 트랜지스터이기 때문에, 현재 반도체 설비를 이용한 양산 공정으로 100% 제작이 가능하며 저비용으로 빠르게 대량생산이 가능하다는 점에서 의미가 크다.

연구를 주도한 김승일 박사과정은 개발된 “암호 반도체로서 초소형/저전력 난수발생기는 특유의 예측 불가능성으로 인해 보안 기능을 강화해 칩 또는 칩 간의 통신 보안으로 안전한 초연결성을 지원할 수 있고, 특히 기존 연구 대비 에너지, 집적도, 비용 측면에서 탁월한 장점을 갖고 있어 사물인터넷(IoT) 기기 환경에 적합하다”고 연구의 의의를 설명했다.

전기및전자공학부 김승일 박사과정이 제1 저자, 유형진 석사가 공저자로 참여한 이번 연구는 국제학술지 ‘사이언스(Science)’의 자매지인 ‘사이언스 어드밴시스(Science Advances)’ 2024년 2월 온라인판에 정식 출판됐다. (논문명 : Cryptographic transistor for true random number generator with low power consumption)

한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 국가반도체연구실지원핵심기술개발사업의 지원을 받아 수행됐다.

2024.02.29 조회수 2502

해킹 공격 막는 암호 반도체 최초 개발

사물인터넷(IoT), 자율 주행 등 5G/6G 시대 소자 또는 기기 간의 상호 정보 교환이 급증함에 따라 해킹 공격이 고도화되고 있다. 이에 따라, 기기에서 데이터를 안전하게 전송하기 위해서는 보안 기능 강화가 필수적이다.

우리 대학 전기및전자공학부 최양규 교수와 류승탁 교수 공동연구팀이 ‘해킹 막는 세계 최초 보안용 암호 반도체’를 개발하는 데 성공했다고 29일 밝혔다.

연구팀은 100% 실리콘 호환 공정으로 제작된 핀펫(FinFET) 기반 보안용 암호반도체 크립토그래픽 트랜지스터(cryptographic transistor, 이하 크립토리스터(cryptoristor))를 세계 최초로 개발했다. 이는 트랜지스터 하나로 이루어진 독창적 구조를 갖고 있을 뿐만 아니라, 동작 방식 또한 독특해 유일무이한 특성을 구비한 난수발생기다.

인공지능 등의 모든 보안 환경에서 가장 중요한 요소는 난수발생기이다. 가장 널리 사용되는 보안 칩인 ‘고급 암호화 표준(advanced encryption standard, AES)’에서 난수발생기는 핵심 요소로, AES 보안 칩 전체 면적의 약 75%, 에너지 소모의 85% 이상을 차지한다. 따라서, 모바일 혹은 사물인터넷(IoT)에 탑재가 가능한 저전력/초소형 난수발생기 개발이 시급하다.

기존의 난수발생기는 전력 소모가 매우 크고 실리콘 CMOS 공정과의 호환성이 떨어진다는 단점이 있고, 회로 기반의 난수발생기들은 점유 면적이 매우 크다는 단점이 있다.

연구팀은 기존 세계 최고 수준 연구 대비 전력 소모와 점유 면적 모두 수천 배 이상 작은 암호 반도체인 단일 소자 기반의 크립토리스터(cryptoristor)를 개발했다. 절연층이 실리콘 하부에 형성되어 있는 실리콘 온 인슐레이터(Silicon-on-Insulator, SOI) 기판 위에 제작된 핀펫(FinFET)이 가지는 내재적인 전위 불안정성을 이용해 무작위적으로 0과 1을 예측 불가능하게 내보내는 난수발생기를 개발했다.

다시 설명하면, 보통 모바일 기기 등에서 정보를 교환할 때 데이터를 암호화하는 알고리즘에는 해커가 암호화한 알고리즘을 예측할 수 없도록 하는 것이 중요하다. 이에 무작위의 0과 1이 난수이며 0과 1의 배열이 매번 다른 결과가 나오게 하여 예측 불가능성을 가지도록 함으로써 공격자가 예측하지 못하도록 차단하는 방식이다.

특히, 크립토리스터 기반 난수발생기 연구는 국제적으로도 구현한 사례가 없는 세계 최초의 연구이면서, 기존 논리 연산용 또는 메모리용 소자와 동일한 구조의 트랜지스터이기 때문에, 현재 반도체 설비를 이용한 양산 공정으로 100% 제작이 가능하며 저비용으로 빠르게 대량생산이 가능하다는 점에서 의미가 크다.

연구를 주도한 김승일 박사과정은 개발된 “암호 반도체로서 초소형/저전력 난수발생기는 특유의 예측 불가능성으로 인해 보안 기능을 강화해 칩 또는 칩 간의 통신 보안으로 안전한 초연결성을 지원할 수 있고, 특히 기존 연구 대비 에너지, 집적도, 비용 측면에서 탁월한 장점을 갖고 있어 사물인터넷(IoT) 기기 환경에 적합하다”고 연구의 의의를 설명했다.

전기및전자공학부 김승일 박사과정이 제1 저자, 유형진 석사가 공저자로 참여한 이번 연구는 국제학술지 ‘사이언스(Science)’의 자매지인 ‘사이언스 어드밴시스(Science Advances)’ 2024년 2월 온라인판에 정식 출판됐다. (논문명 : Cryptographic transistor for true random number generator with low power consumption)

한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 국가반도체연구실지원핵심기술개발사업의 지원을 받아 수행됐다.

2024.02.29 조회수 2502 -

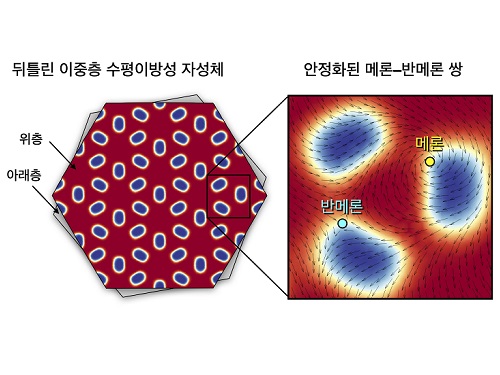

차세대 반도체 솔리톤 안정화 기술 최초 개발

초고속 초저전력 차세대 반도체 기술을 구현할 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 기술이 개발되었다.

우리 대학 물리학과 김세권 교수 연구팀이 기초과학연구원 복잡계 이론물리 연구단(PCS-IBS) 김경민 박사팀, 한양대학교 물리학과 박문집 교수팀과의 공동 연구로 뒤틀림 자성체*를 이용해 위상적 솔리톤을 안정화시킬 수 있는 기술을 세계 최초로 개발해 물리 및 화학 분야 세계적인 학술지 `나노 레터스(Nano Letters)'에 게재했다고 20일 밝혔다.

*자성체: 자성을 띄는 여러 물체를 통칭함

스핀트로닉스는 성장 한계에 다다른 기존 반도체 기술의 근본적인 문제점들을 전자의 양자적 성질인 스핀을 이용해 해결하고자 하는 연구 분야다. 이는 기존 정보처리 기술을 혁신적으로 발전시켜 초고속 초저전력 차세대 반도체 기술을 구현할 것으로 기대되고 있다.

한편 솔리톤이란 특정한 구조가 주변과 상호작용을 통해 사라지지 않고 계속 유지하는 현상을 말하며, 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 개발이 전 세계 각국 학계와 산업계에서 경쟁적으로 연구가 이뤄지고 있다.

이전까지 차세대 메모리 소자 개발을 위해 연구됐던 위상적 솔리톤으로는 스핀 구조체로 자연계에 존재하는 다양한 자성체 중 수직 이방성*이라고 하는 특수한 성질을 갖는 자성체에서만 안정하다고 알려져, 물질 선택의 제한으로 인해 솔리톤 기반 정보처리 기술 발전에 어려움이 있었다.

* 수직 이방성: 자화 방향이 자성체에 수직한 방향을 선호하게 되는 성질

김세권 교수 연구팀은 특정 단층 강자성체* 두 겹을 서로 뒤틀어 접합시켜 이중층 자성체를 구성할 경우, 수직 이방성을 띠지 않는 다른 종류의 자성체에서도 위상적 솔리톤을 안정화시킬 수 있음을 세계 최초로 발견했다.

*강자성체: 자성체 중에서도 상온의 철과 같이 자발적 자화를 띄는 물체를 뜻함

이번 연구를 통해 발견된 안정한 위상적 솔리톤은 수직이방성이 아닌 수평 이방성을 띄는 자성체에 존재하는 ‘메론’이라고 불리는 스핀 구조체로서 이전에는 그 안정화 메커니즘이 알려지지 않았던 솔리톤이다. 메론 안정화 기술의 확보로 지금까지 수직 이방성 자성체에만 국한되어 있었던 솔리톤 기반 차세대 반도체 기술 연구를 다양한 자성체로 확대 발전시킬 수 있을 것으로 기대되며, 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 작용할 것으로 예상된다.

이번 연구 결과는 자성체 내부에서는 안정하지 않은 위상적 솔리톤이 두 자성체를 뒤틀어 접합할 경우, 자성체 간 상호작용을 통해 안정화될 수 있다는 것을 보인 첫 예시다. 여러 자성체를 뒤틀어 접합시키는 경우 자성체의 종류와 뒤틀림 각도를 조절함으로써 무한히 많은 자성 시스템을 구현할 수 있으므로, 이번 연구 결과는 뒤틀림 자성체 기반 스핀 기술이라고 하는 넓은 연구 영역을 새로이 개척했다고 판단된다.

우리 대학 김세권 교수는 "이번 논문은 무한히 많은 가능성을 갖는 뒤틀림 자성체 기반의 새로운 물리 현상 탐색과 활용 연구의 시발점으로 작용할 것ˮ이라고 기대감을 내비쳤다.

이번 연구는 우리 대학 김세권 교수, 우리 대학 고경춘 박사, 그리고 PCS-IBS 김경민 박사, 한양대학교 박문집 교수의 공동 연구로 진행되었으며, 한국연구재단 해외우수과학자 유치사업 플러스(브레인 풀 플러스)의 지원을 받아 수행됐다.

2024.02.20 조회수 1955

차세대 반도체 솔리톤 안정화 기술 최초 개발

초고속 초저전력 차세대 반도체 기술을 구현할 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 기술이 개발되었다.

우리 대학 물리학과 김세권 교수 연구팀이 기초과학연구원 복잡계 이론물리 연구단(PCS-IBS) 김경민 박사팀, 한양대학교 물리학과 박문집 교수팀과의 공동 연구로 뒤틀림 자성체*를 이용해 위상적 솔리톤을 안정화시킬 수 있는 기술을 세계 최초로 개발해 물리 및 화학 분야 세계적인 학술지 `나노 레터스(Nano Letters)'에 게재했다고 20일 밝혔다.

*자성체: 자성을 띄는 여러 물체를 통칭함

스핀트로닉스는 성장 한계에 다다른 기존 반도체 기술의 근본적인 문제점들을 전자의 양자적 성질인 스핀을 이용해 해결하고자 하는 연구 분야다. 이는 기존 정보처리 기술을 혁신적으로 발전시켜 초고속 초저전력 차세대 반도체 기술을 구현할 것으로 기대되고 있다.

한편 솔리톤이란 특정한 구조가 주변과 상호작용을 통해 사라지지 않고 계속 유지하는 현상을 말하며, 위상적 솔리톤이라는 구조체를 이용해 정보를 저장하고 전송할 수 있는 초고속 비휘발성 메모리 소자 개발이 전 세계 각국 학계와 산업계에서 경쟁적으로 연구가 이뤄지고 있다.

이전까지 차세대 메모리 소자 개발을 위해 연구됐던 위상적 솔리톤으로는 스핀 구조체로 자연계에 존재하는 다양한 자성체 중 수직 이방성*이라고 하는 특수한 성질을 갖는 자성체에서만 안정하다고 알려져, 물질 선택의 제한으로 인해 솔리톤 기반 정보처리 기술 발전에 어려움이 있었다.

* 수직 이방성: 자화 방향이 자성체에 수직한 방향을 선호하게 되는 성질

김세권 교수 연구팀은 특정 단층 강자성체* 두 겹을 서로 뒤틀어 접합시켜 이중층 자성체를 구성할 경우, 수직 이방성을 띠지 않는 다른 종류의 자성체에서도 위상적 솔리톤을 안정화시킬 수 있음을 세계 최초로 발견했다.

*강자성체: 자성체 중에서도 상온의 철과 같이 자발적 자화를 띄는 물체를 뜻함

이번 연구를 통해 발견된 안정한 위상적 솔리톤은 수직이방성이 아닌 수평 이방성을 띄는 자성체에 존재하는 ‘메론’이라고 불리는 스핀 구조체로서 이전에는 그 안정화 메커니즘이 알려지지 않았던 솔리톤이다. 메론 안정화 기술의 확보로 지금까지 수직 이방성 자성체에만 국한되어 있었던 솔리톤 기반 차세대 반도체 기술 연구를 다양한 자성체로 확대 발전시킬 수 있을 것으로 기대되며, 스핀트로닉스 기술을 한 단계 성장시키는 원동력으로 작용할 것으로 예상된다.

이번 연구 결과는 자성체 내부에서는 안정하지 않은 위상적 솔리톤이 두 자성체를 뒤틀어 접합할 경우, 자성체 간 상호작용을 통해 안정화될 수 있다는 것을 보인 첫 예시다. 여러 자성체를 뒤틀어 접합시키는 경우 자성체의 종류와 뒤틀림 각도를 조절함으로써 무한히 많은 자성 시스템을 구현할 수 있으므로, 이번 연구 결과는 뒤틀림 자성체 기반 스핀 기술이라고 하는 넓은 연구 영역을 새로이 개척했다고 판단된다.

우리 대학 김세권 교수는 "이번 논문은 무한히 많은 가능성을 갖는 뒤틀림 자성체 기반의 새로운 물리 현상 탐색과 활용 연구의 시발점으로 작용할 것ˮ이라고 기대감을 내비쳤다.

이번 연구는 우리 대학 김세권 교수, 우리 대학 고경춘 박사, 그리고 PCS-IBS 김경민 박사, 한양대학교 박문집 교수의 공동 연구로 진행되었으며, 한국연구재단 해외우수과학자 유치사업 플러스(브레인 풀 플러스)의 지원을 받아 수행됐다.

2024.02.20 조회수 1955 -

반도체가 곤충처럼 사물 움직임 감지한다

곤충의 시신경계를 모방하여 초고속, 저전력 동작이 가능한 신개념 ‘지능형 센서’ 반도체의 개발로 다양한 혁신적 기술로 확장가능한 기술이 개발되었다. 이 기술은 교통, 안전, 보안 시스템 등 다양한 분야에 응용되어 산업과 사회에 기여할 것으로 보인다.

우리 대학 신소재공학과 김경민 교수 연구팀이 다양한 멤리스터* 소자를 융합해 곤충의 시신경에서의 시각 지능*을 모사하는 지능형 동작인식 소자를 개발하는데 성공했다고 19일 밝혔다.

*멤리스터 (Memristor): 메모리(Memory)와 저항(Resistor)의 합성어로, 입력 신호에 따라 소자의 저항 상태가 변하는 전자소자.

*시각 지능 (Visual Intelligence): 시신경 내에서 시각 정보를 해석하고 연산을 수행하는 기능.

최근 인공지능(AI) 기술의 발전과 함께, 비전 시스템은 이미지 인식, 객체 탐지 및 동작 분석과 같은 다양한 작업에서 AI를 활용해 핵심적인 역할을 수행하고 있다. 하지만 기존 비전 시스템은 이미지 센서에서 수신된 신호를 복잡한 알고리즘을 이용해 물체와 그 동작을 인식하는 것이 일반적이다. 이러한 방식은 상당한 양의 데이터 트래픽과 높은 전력 소모가 필요하여 모바일 또는 사물인터넷 장치에 적용되기 어렵다.

한편, 곤충은 기본 동작 감지기(Elementary Motion Detector) 라는 시신경 회로를 통해 시각 정보를 효과적으로 처리해 물체를 탐지하고 그 동작을 인식하는데 탁월한 능력을 보인다. <그림1> 이를 구현하는 데 있어 기존 실리콘 집적회로(CMOS) 기술에서는 복잡한 회로가 요구되기 때문에, 실제 소자로 제작하기 어려운 한계가 있었다.

김경민 교수 연구팀은 다양한 기능의 멤리스터 소자들을 집적하여 고효율⋅초고속 동작 인식이 가능한 지능형 동작인식 소자를 개발했다. 동작인식 소자는 자체 개발한 두 종류의 멤리스터 소자와 저항 만으로 구성된 단순한 구조를 가지고 있다. 두 종류의 서로 다른 멤리스터는 각각 신호 지연 기능과 신호 통합 및 발화 기능을 수행하며, 이를 통해 곤충의 시신경을 직접 모사하여 사물의 움직임을 판단할 수 있음을 확인했다. <그림2>

연구팀은 개발된 동작인식 소자의 실질적인 활용에 대한 가능성을 입증하기 위해 차량 경로를 예측하는 뉴로모픽 컴퓨팅 시스템을 설계하였으며, 여기에 개발한 동작인식 소자를 적용하였다. <그림3> 그 결과 기존 기술 대비 에너지 소비를 92.9 % 감소하여 더 정확히 사물의 움직임을 예측할 수 있음을 검증하였다.

신소재공학과 김경민 교수는 “곤충은 매우 간단한 시각 지능을 활용해 놀랍도록 민첩하게 물체의 동작을 인지하는데, 이번 연구는 신경의 기능을 재현할 수 있는 멤리스터 소자를 활용해 이를 구현할 수 있었다는 점에 큰 의의가 있다”며, “최근 AI가 탑재된 휴대폰과 같이 에지(edge)형 인공지능 소자의 중요성이 매우 커지고 있는데, 이 연구는 동작 인식을 위한 효율적인 비전 시스템 구현에 기여할 수 있어, 향후 자율주행 자동차, 차량 운송 시스템, 로봇, 머신 비전 등과 같은 다양한 분야에 적용될 수 있을 것으로 기대된다”고 밝혔다.

이번 연구는 신소재공학과 송한찬 박사과정, 이민구 박사과정 학생이 공동 제1 저자로 참여했으며, 국제 학술지 ‘어드밴스드 머티리얼즈(Advanced Materials, IF: 29.4)’에 지난 1월 29일 字 온라인 게재됐다.

한편 이번 연구는 한국연구재단 중견연구사업, 차세대지능형반도체기술개발사업, PIM인공지능반도체핵심기술개발사업, 나노종합기술원 및 KAIST 도약연구사업의 지원을 받아 수행됐다. (논문명: Fully Memristive Elementary Motion Detectors for A Maneuver Prediction, 논문링크: https://doi.org/10.1002/adma.202309708)

2024.02.19 조회수 2557

반도체가 곤충처럼 사물 움직임 감지한다

곤충의 시신경계를 모방하여 초고속, 저전력 동작이 가능한 신개념 ‘지능형 센서’ 반도체의 개발로 다양한 혁신적 기술로 확장가능한 기술이 개발되었다. 이 기술은 교통, 안전, 보안 시스템 등 다양한 분야에 응용되어 산업과 사회에 기여할 것으로 보인다.

우리 대학 신소재공학과 김경민 교수 연구팀이 다양한 멤리스터* 소자를 융합해 곤충의 시신경에서의 시각 지능*을 모사하는 지능형 동작인식 소자를 개발하는데 성공했다고 19일 밝혔다.

*멤리스터 (Memristor): 메모리(Memory)와 저항(Resistor)의 합성어로, 입력 신호에 따라 소자의 저항 상태가 변하는 전자소자.

*시각 지능 (Visual Intelligence): 시신경 내에서 시각 정보를 해석하고 연산을 수행하는 기능.

최근 인공지능(AI) 기술의 발전과 함께, 비전 시스템은 이미지 인식, 객체 탐지 및 동작 분석과 같은 다양한 작업에서 AI를 활용해 핵심적인 역할을 수행하고 있다. 하지만 기존 비전 시스템은 이미지 센서에서 수신된 신호를 복잡한 알고리즘을 이용해 물체와 그 동작을 인식하는 것이 일반적이다. 이러한 방식은 상당한 양의 데이터 트래픽과 높은 전력 소모가 필요하여 모바일 또는 사물인터넷 장치에 적용되기 어렵다.

한편, 곤충은 기본 동작 감지기(Elementary Motion Detector) 라는 시신경 회로를 통해 시각 정보를 효과적으로 처리해 물체를 탐지하고 그 동작을 인식하는데 탁월한 능력을 보인다. <그림1> 이를 구현하는 데 있어 기존 실리콘 집적회로(CMOS) 기술에서는 복잡한 회로가 요구되기 때문에, 실제 소자로 제작하기 어려운 한계가 있었다.

김경민 교수 연구팀은 다양한 기능의 멤리스터 소자들을 집적하여 고효율⋅초고속 동작 인식이 가능한 지능형 동작인식 소자를 개발했다. 동작인식 소자는 자체 개발한 두 종류의 멤리스터 소자와 저항 만으로 구성된 단순한 구조를 가지고 있다. 두 종류의 서로 다른 멤리스터는 각각 신호 지연 기능과 신호 통합 및 발화 기능을 수행하며, 이를 통해 곤충의 시신경을 직접 모사하여 사물의 움직임을 판단할 수 있음을 확인했다. <그림2>

연구팀은 개발된 동작인식 소자의 실질적인 활용에 대한 가능성을 입증하기 위해 차량 경로를 예측하는 뉴로모픽 컴퓨팅 시스템을 설계하였으며, 여기에 개발한 동작인식 소자를 적용하였다. <그림3> 그 결과 기존 기술 대비 에너지 소비를 92.9 % 감소하여 더 정확히 사물의 움직임을 예측할 수 있음을 검증하였다.

신소재공학과 김경민 교수는 “곤충은 매우 간단한 시각 지능을 활용해 놀랍도록 민첩하게 물체의 동작을 인지하는데, 이번 연구는 신경의 기능을 재현할 수 있는 멤리스터 소자를 활용해 이를 구현할 수 있었다는 점에 큰 의의가 있다”며, “최근 AI가 탑재된 휴대폰과 같이 에지(edge)형 인공지능 소자의 중요성이 매우 커지고 있는데, 이 연구는 동작 인식을 위한 효율적인 비전 시스템 구현에 기여할 수 있어, 향후 자율주행 자동차, 차량 운송 시스템, 로봇, 머신 비전 등과 같은 다양한 분야에 적용될 수 있을 것으로 기대된다”고 밝혔다.

이번 연구는 신소재공학과 송한찬 박사과정, 이민구 박사과정 학생이 공동 제1 저자로 참여했으며, 국제 학술지 ‘어드밴스드 머티리얼즈(Advanced Materials, IF: 29.4)’에 지난 1월 29일 字 온라인 게재됐다.

한편 이번 연구는 한국연구재단 중견연구사업, 차세대지능형반도체기술개발사업, PIM인공지능반도체핵심기술개발사업, 나노종합기술원 및 KAIST 도약연구사업의 지원을 받아 수행됐다. (논문명: Fully Memristive Elementary Motion Detectors for A Maneuver Prediction, 논문링크: https://doi.org/10.1002/adma.202309708)

2024.02.19 조회수 2557 -

차세대 2차원 반도체 다기능 전자 소자 개발

공급 전압에 의한 2차원 반도체의 극성 전환을 이용해 새로운 전자 소자로의 응용이 보고된 바 있으나, 모두 누설 전류가 크거나 낮은 전류점멸비로 인해 실제 집적 회로(IC)칩에서 사용하기 어려웠다. 우리 대학 연구팀은 다기능 전자 소자를 통해 프로그램 및 기능성 변환이 가능한 회로 구현의 가능성을 제시하고 IC칩에서의 2차원 반도체의 활용성을 확장하는 기술을 개발하였다.

우리 대학 전기및전자공학부 이가영 교수 연구팀이 양극성 반도체 특성을 가진 2차원 나노 반도체 기반의 다기능 전자 소자를 개발했다고 2일 밝혔다. 다기능 전자 소자란 기존 트랜지스터와 달리 전압에 따라 기능을 변환할 수 있는 소자로, 연구팀의 소자는 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광 감지 소자로 변환 가능하여 폭 넓은 사용이 가능하다.

기존 실리콘 반도체보다 성능이 뛰어난 이황화 몰리브덴(MoS2)는 층상 구조의 2차원 반도체 나노 소재로, 전자가 흐르는 N형 반도체 특성을 가지면서 대기에서 안정적이다. 또한, 기존 실리콘 반도체가 미세화될수록 성능 저하에 취약함에 반해, 이황화 몰리브덴은 관련 문제가 적어 차세대 반도체로서 학계뿐만 아니라 삼성, TSMC, 인텔과 같은 산업계에서의 연구도 활발하다.

그러나 상보적 금속산화막 반도체(CMOS) 구현을 위해서는 음(N) 전하를 띄는 전자뿐만 아니라 양(P) 전하를 띄는 정공 유도도 필요한 데, 이황화 몰리브덴에서는 정공 유도가 어려웠다. 이 문제를 해결하기 위해 이황화 몰리브덴에 추가적인 공정을 도입하거나 다른 P형 물질을 사용하는 방법이 시도됐으나, 공정 난이도가 높다. 이러한 문제점은 현재까지도 이황화 몰리브덴을 상용화하기 위해 해결해야 할 중요한 과제로 남아 있다.

이가영 교수 연구팀은 채널 하부에 전극을 배치하고 금속/반도체 접합 특성을 개선해 전자와 정공 모두 선택적으로 흐를 수 있는 양극성 특성을 구현하는 데 성공했다. 이로써 전류의 점멸 비율을 대폭 높일 뿐만 아니라, 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광감지 소자로 다기능 변조 동작이 가능한 이황화 몰리브덴 전자 소자를 개발했다. 또한 이를 기반으로 집적도가 개선된 논리 연산이 가능함도 보였다.

이번 연구를 주도한 송준기, 이수연 학생은 “기존 실리콘 금속산화막 반도체(CMOS) 공정 호환성이 높은 공정 과정을 통해 차세대 2차원 반도체의 다양한 기능을 구현했다”며 “IC칩에서 이황화 몰리브덴의 전자소자로의 활용성 및 실용성을 넓히는 계기가 될 것이다”라고 덧붙였다.

이가영 교수는 “이번에 개발한 전자 소자는 주어진 전압 특성에 따라 다양한 기능을 수행하면서도 각 기능의 성능이 우수하다”며 “서로 다른 기능의 소자들은 대개 구조와 공정 방법들이 달라 함께 집적시 공정 난이도가 높고 회로 도면 변화에 따른 공정 전환이 까다롭다. 반면, 이번에 개발한 신개념 소자는 하나의 소자에서 다기능을 할 수 있어서 현재 수요가 급증하고 있는 맞춤형 반도체의 제작 및 공정 전환을 용이하게 할 것이다. 목적에 따라 회로 자체의 기능성을 변환할 수 있어 단일 칩 시스템의 소형화에도 기여할 것으로 기대한다”라고 말했다.

우리 대학 전기및전자공학부 송준기 석박통합과정 학생과 이수연 석사과정 학생이 공동 제1 저자로 참여한 이번 연구는 나노과학 분야 저명 국제 학술지 `ACS Nano'에 2024년 1월 26일 온라인판에 출판됐다. (논문명 : Drain-induced multifunctional ambipolar electronics based on junctionless MoS2)

한편 이번 연구는 한국연구재단의 기초연구사업 및 BK21, KAIST의 C2 사업, 그리고 LX 세미콘-KAIST 미래기술센터의 지원을 받아 수행됐다.

2024.02.05 조회수 2149

차세대 2차원 반도체 다기능 전자 소자 개발

공급 전압에 의한 2차원 반도체의 극성 전환을 이용해 새로운 전자 소자로의 응용이 보고된 바 있으나, 모두 누설 전류가 크거나 낮은 전류점멸비로 인해 실제 집적 회로(IC)칩에서 사용하기 어려웠다. 우리 대학 연구팀은 다기능 전자 소자를 통해 프로그램 및 기능성 변환이 가능한 회로 구현의 가능성을 제시하고 IC칩에서의 2차원 반도체의 활용성을 확장하는 기술을 개발하였다.

우리 대학 전기및전자공학부 이가영 교수 연구팀이 양극성 반도체 특성을 가진 2차원 나노 반도체 기반의 다기능 전자 소자를 개발했다고 2일 밝혔다. 다기능 전자 소자란 기존 트랜지스터와 달리 전압에 따라 기능을 변환할 수 있는 소자로, 연구팀의 소자는 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광 감지 소자로 변환 가능하여 폭 넓은 사용이 가능하다.

기존 실리콘 반도체보다 성능이 뛰어난 이황화 몰리브덴(MoS2)는 층상 구조의 2차원 반도체 나노 소재로, 전자가 흐르는 N형 반도체 특성을 가지면서 대기에서 안정적이다. 또한, 기존 실리콘 반도체가 미세화될수록 성능 저하에 취약함에 반해, 이황화 몰리브덴은 관련 문제가 적어 차세대 반도체로서 학계뿐만 아니라 삼성, TSMC, 인텔과 같은 산업계에서의 연구도 활발하다.

그러나 상보적 금속산화막 반도체(CMOS) 구현을 위해서는 음(N) 전하를 띄는 전자뿐만 아니라 양(P) 전하를 띄는 정공 유도도 필요한 데, 이황화 몰리브덴에서는 정공 유도가 어려웠다. 이 문제를 해결하기 위해 이황화 몰리브덴에 추가적인 공정을 도입하거나 다른 P형 물질을 사용하는 방법이 시도됐으나, 공정 난이도가 높다. 이러한 문제점은 현재까지도 이황화 몰리브덴을 상용화하기 위해 해결해야 할 중요한 과제로 남아 있다.

이가영 교수 연구팀은 채널 하부에 전극을 배치하고 금속/반도체 접합 특성을 개선해 전자와 정공 모두 선택적으로 흐를 수 있는 양극성 특성을 구현하는 데 성공했다. 이로써 전류의 점멸 비율을 대폭 높일 뿐만 아니라, 양극성 트랜지스터, N형 트랜지스터, 다이오드, 항복 다이오드 그리고 광감지 소자로 다기능 변조 동작이 가능한 이황화 몰리브덴 전자 소자를 개발했다. 또한 이를 기반으로 집적도가 개선된 논리 연산이 가능함도 보였다.

이번 연구를 주도한 송준기, 이수연 학생은 “기존 실리콘 금속산화막 반도체(CMOS) 공정 호환성이 높은 공정 과정을 통해 차세대 2차원 반도체의 다양한 기능을 구현했다”며 “IC칩에서 이황화 몰리브덴의 전자소자로의 활용성 및 실용성을 넓히는 계기가 될 것이다”라고 덧붙였다.

이가영 교수는 “이번에 개발한 전자 소자는 주어진 전압 특성에 따라 다양한 기능을 수행하면서도 각 기능의 성능이 우수하다”며 “서로 다른 기능의 소자들은 대개 구조와 공정 방법들이 달라 함께 집적시 공정 난이도가 높고 회로 도면 변화에 따른 공정 전환이 까다롭다. 반면, 이번에 개발한 신개념 소자는 하나의 소자에서 다기능을 할 수 있어서 현재 수요가 급증하고 있는 맞춤형 반도체의 제작 및 공정 전환을 용이하게 할 것이다. 목적에 따라 회로 자체의 기능성을 변환할 수 있어 단일 칩 시스템의 소형화에도 기여할 것으로 기대한다”라고 말했다.

우리 대학 전기및전자공학부 송준기 석박통합과정 학생과 이수연 석사과정 학생이 공동 제1 저자로 참여한 이번 연구는 나노과학 분야 저명 국제 학술지 `ACS Nano'에 2024년 1월 26일 온라인판에 출판됐다. (논문명 : Drain-induced multifunctional ambipolar electronics based on junctionless MoS2)

한편 이번 연구는 한국연구재단의 기초연구사업 및 BK21, KAIST의 C2 사업, 그리고 LX 세미콘-KAIST 미래기술센터의 지원을 받아 수행됐다.

2024.02.05 조회수 2149