인물

< (왼쪽부터) 조윤서 박사과정, 박선의 박사과정, 방주은 박사과정 >

우리 대학 전기및전자공학부 최재혁 교수 연구실(연구실명: 집적회로 시스템 연구실, Integrated Circuits and System Lab)에서 ‘제22회 대한민국 반도체 설계대전’의 대통령상 수상자를 배출했다.

‘제22회 대한민국 반도체 설계대전’은 산업통상자원부와 한국반도체산업협회가 공동으로 주관하는 반도체 설계 전문 공모전으로, 반도체 설계분야 대학(원)생들의 설계 능력을 배양하고, 창의적인 아이디어를 발굴하는 것을 목표로 한다.

대통령상 수상자는 최재혁 교수 연구실의 박선의 박사과정, 조윤서 박사과정, 방주은 박사과정 학생으로 6G 통신에서 통신을 방해하는 잡음(noise)을 획기적으로 낮추는 ‘초 저잡음 신호’를 생성할 수 있는 CMOS(상보형금속산화반도체) 공정 기반의 칩을 개발해 대통령상에 선정됐다.

6G 통신은 최대 20 기가bps(Gbps)의 전송 속도를 갖는 5G 통신 대비 최대 50배 빠른 1 테라bps(Tbps)를 목표로 연구가 진행되고 있다. 일반적으로 통신 주파수 대역이 올라갈수록 넓은 통신 대역폭을 사용할 수 있어 데이터 전송 속도를 높일 수 있기 때문에, 6G 통신에서 요구하는 높은 데이터 전송 속도를 위해서는 100 기가헤르츠(GHz) 이상 주파수 대역의 사용이 필수적이다.

하지만, 이러한 높은 주파수 대역에서 반송파로 사용될 수 있는 정확한 기준 신호를 CMOS 공정을 이용해 만드는 것은 큰 난제였다. CMOS 공정이 초소형, 저전력 디자인에 유리함에도 불구하고, 그 동작 주파수와 고주파 대역 이득(gain)에 한계가 있고, 저잡음 특성이 SiGe, InP 등의 현존하는 다른 공정에 비해 불리하기 때문에 100 기가헤르츠(GHz) 이상의 주파수 대역에서 초 저잡음 성능을 달성하기 어려웠기 때문이다.

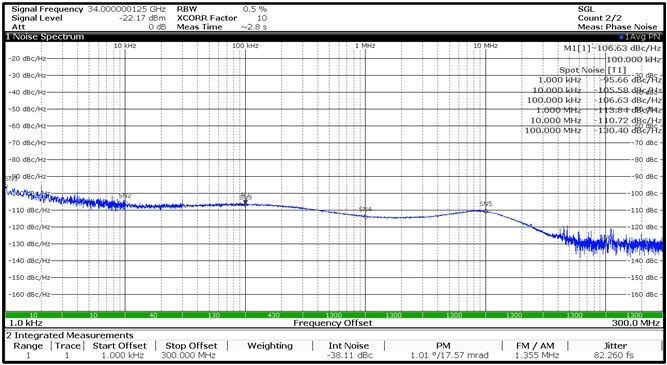

하지만, 최재혁 교수팀 학생들이 개발한 칩에서는 이러한 한계를 극복하고, CMOS 공정을 사용해 처음으로 100 기가헤르츠(GHz) 이상 대역에서 고차 변‧복조 기술을 지원할 수 있는 초 저잡음 신호 생성 기술을 선보였다. 이 기술은 CMOS 공정 기반으로도 6G 통신에서 요구하는 초 저잡음 성능을 달성할 수 있다는 것을 보여줌으로써, 장차 상용화될 6G 통신 칩의 가격 경쟁력과 집적도를 높이는 데 기여할 것으로 기대된다.

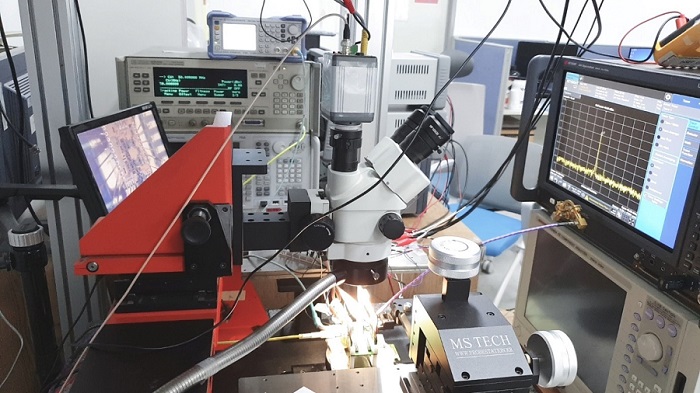

< 측정 진행 사진 >

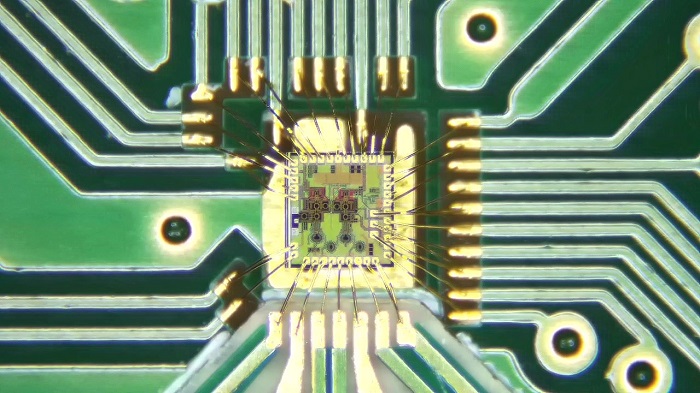

< 현미경으로 관찰한 칩 사진 >

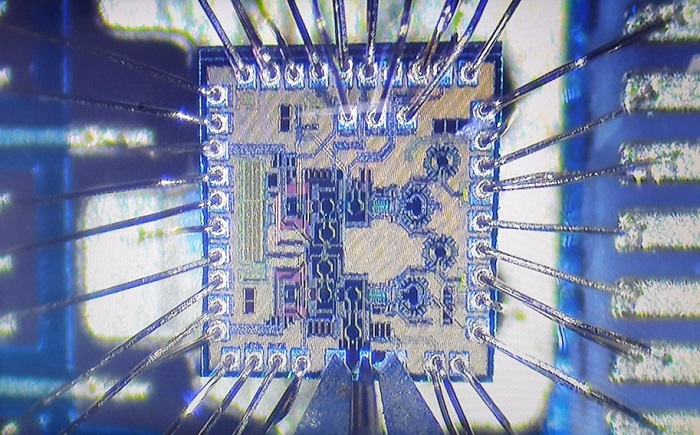

< 현미경으로 관찰한 칩 사진(더 확대된 사진) >

< 측정 결과 사진: 위상 잡음 분석기를 사용해 측정된 위상 잡음 결과 >

대통령상 수상팀에게는 상금 500만 원과 부상이 수여되며, 시상식은 11월 22일 코엑스에서 진행된다.

-

인물 최신현 교수, 올해의 현우 KAIST 학술상 수상

우리 대학 전기및전자공학부 최신현 교수가 차세대 AI 하드웨어 개발 및 혁신적인 반도체 관련 연구 성과로, KAIST가 주관하고 현우문화재단(이사장 곽수일)이 후원하는 `현우 KAIST 학술상' 수상자로 선정됐다. 수상자로 선정된 최신현 교수의 중점 연구 분야는 미래형 메모리와 컴퓨터 장치 개발에 집중한 ▶저항 스위칭 소자(resistive switching device)를 이용해 기본 방식보다 더 빠르고 효율적인 차세대 메모리·컴퓨팅 장치 개발, ▶엣지 컴퓨팅(edge computing)과 뉴로모픽 컴퓨팅(neuromorphic computing)의 스마트한 컴퓨터 메모리 기능 등 통합 시스템 응용, ▶기존 3단자 트랜지스터(3-terminal transistor) 방식과 다른 더 효율적이고 창의적인 컴퓨팅·메모리 소자 작동 방식 개발이다. 대표적인 연구 업적으로 차세대 메모리 기술 분야에서 기존의 값비싼 초미세 노광공정*을 사용하는 방식보다 전기

2025-05-02 -

연구 고성능 촉매 개발, 반도체 핫전자 기술을 통해 해결하다

우리 대학 화학과 박정영 석좌교수, 신소재공학과 정연식 교수, 그리고 KIST 김동훈 박사 공동 연구팀이 반도체 기술을 활용하여 촉매 성능에 특정 변인이 미치는 영향을 정량적으로 분석할 수 있는 새로운 플랫폼을 성공적으로 구현했다. 이를 통해 대표적인 다경로 화학 반응인 메탄올 산화 반응에서 메틸 포르메이트 선택성을 크게 향상시켰으며, 이번 연구는 차세대 고성능 이종 촉매 개발을 앞당기는 데 기여할 것으로 기대된다고 1일 밝혔다. 다경로 화학 반응에서는 반응성과 선택성의 상충 관계로 인해 특정 생성물의 선택성을 높이는 것이 어려운 문제로 남아 있다. 특히, 메탄올 산화 반응에서는 이산화탄소와 더불어 고부가 가치 생성물인 메틸 포르메이트가 생성되므로, 메틸 포르메이트의 선택성을 극대화하는 것이 중요하다. 그러나 기존 불규칙적인 구조의 이종 촉매에서는 금속-산화물 계면 밀도를 비롯한 여러 변인이 동시에 촉매 성능에 영향을 미치기 때문에 특정 변수가 개별적으로 미치는 영향을 분

2025-04-01 -

행사 인공지능반도체대학원, 제2회 한국인공지능시스템포럼 AI 산업혁신 논의

우리 대학 인공지능반도체대학원 주최로 20일(목) 오전 대전 오노마 호텔에서 ‘제2회 한국인공지능시스템포럼(KAISF) 조찬 강연회’가 성황리에 개최되었다. 본 행사는 인공지능(AI) 기술의 최신 동향과 혁신 및 응용, 특히 AI-X(AI-특정산업)에 대해 다양한 분야의 전문가들이 모여 심도 있는 논의를 진행하는 자리로 LG AI 연구원의 최정규 상무가 LLM(거대언어모델)에 대해 개발에 대해 발표한다. 조찬 회의에는 총 65명의 AI 전문가가 참석하였으며, LG AI 연구원에서 최근 개발하고 공개한 대규모 언어 모델인 ‘엑사원(EXAONE)에 대해 Driving the Future of AI Innovation’라는 주제로 발제 발표가 진행되었다. 최정규 LG AI 연구원 상무는 LG 엑사원의 현재 연구 현황과 향후 글로벌 AI 시장에서의 계획을 발표하였으며 특히 최근 AI 생태계를 뜨겁게 달구고 있는 ‘딥시크(Deep

2025-03-20 -

연구 최대 11배 빨라진 PIM 반도체 네트워크 개발

최근 인공지능, 빅데이터, 생명과학 등 연구에 사용되는 메모리 대역폭이 차지하는 비중이 높아, 메모리 내부에 연산장치를 배치하는 프로세싱-인-메모리(Processing-in-Memory, 이하 PIM) 반도체에 대한 연구개발이 활발히 진행되고 있다. 국제 공동 연구진이 기존의 PIM 반도체가 내부장치를 활용하면서도 통신을 할때 반드시 PIM 반도체 외부로 연결되는 CPU를 통해야한다는 문제점으로 발생한 병목현상을 해결했다. 우리 대학 전기및전자공학부 김동준 교수 연구팀이 미국 노스이스턴 대학(Northeastern Univ.), 보스턴 대학(Boston Univ.)와 스페인 무르시아 대학(Universidad de Murcia)의 저명 연구진과‘PIM 반도체 간 집합 통신에 특화된 인터커넥션 네트워크 아키텍처’를 통한 공동연구로 PIM 반도체의 통신 성능을 비약적으로 향상하는 기법을 개발했다고 19일 밝혔다. 김동준 교수 연구팀은 기존 PIM 반도체가

2025-02-19 -

인물 김정호 교수, 한국반도체학술대회 ‘2025 강대원 상’ 수상

우리 대학 전기및전자공학부 김정호 교수가 회로·시스템 분야 '2025년 강대원 상'을 한국반도체학술대회 상임운영위원회로부터 수상한다. 김 교수는 HBM 개발에 기여한 공로를 인정받아 SK하이닉스 이강욱 부사장과 함께 수상한다. 시상식은 13일 오후 강원도 하이원그랜드호텔에서 한국반도체산업협회 · 한국반도체연구조합 · DB하이텍이 공동으로 주관, 개최하는 ‘제32회 한국반도체학술대회(KCS 2025)’ 개막식에서 진행된다. 강대원 상은 세계 최초로 모스펫(MOSFET)과 플로팅게이트를 개발해, 반도체 기술 발전에 신기원을 이룩한 고(故) 강대원 박사를 기리기 위해 제정되었으며, 한국반도체학술대회 상임운영위원회가 지난 2017년 열린 제24회 반도체 학술대회부터 강대원 박사를 이을 인재들을 발굴, 선정해서 시상하고 있다. 김정호 교수는 ‘HBM 아버지’로 불리는 인공지능 반도체 분야의 세계적 권위

2025-02-12