-

문화기술대학원, 제4회 디지털유산 국제심포지엄 개최

우리 대학이 23일(목)부터 이틀간 '제4회 디지털유산 국제심포지엄 개최(The 4th International Symposium on Digital Heritage; ISDH)'을 학술문화관 양승택 오디토리움에서 개최한다.'데이터로서의 문화유산: 유산 보존 관리 및 활용을 위한 디지털 방법론 개발을 선도하는 데이터 중심의 접근 전략'을 주제로 열리는 이번 심포지엄은 문화재청이 주최하고 우리 대학 문화기술대학원이 주관해 디지털헤리티지랩(안재홍, 심혜승)에서 총괄을 맡았다. 특히 이번 행사는 2025년 CIPA 심포지엄*을 우리 대학이 문화재청과 함께 한국에 유치한 것을 기념하기 위해 기획됐다. *CIPA(International Committee of Architectural Photogrammetry) 심포지엄: 1971년 시작되어 현재 2년마다 개최되는 학술대회로, 고고학, 건축학, 보존과학, 디지털 유산 등에서 최신 연구와 기술을 공유하기 위해 다양한 국가와 전문가들이 참여한다. 이를 위해, 디지털유산 분야에서 활발하게 활동하고 있는 국내외 석학 12명이 강연자로 참여한다. 행사 첫날에는 '비전과 미래: 데이터와 문화유산 보존 관리와 활용'을 주제로 한 플레너리 세션과 '데이터로서의 문화유산'을 주제로 한 전문가 토론, 특별 세션이 진행된다.

유럽 타임머신 프로젝트 독일 대사인 샌더 뮨스터(Sander Munster) 독일 프리드리히 실러 예나 대학교 디지털인문학과 교수, 이원재 문화기술대학원 교수, 첸양(Chen Yang) 중국 통지대학교 건축도시계획대학 부교수 겸 호주 퀸즐랜드대학교 건축학부 명예 선임연구원, 유정민 한국전통문화대학교 문화유산산업학과 교수 등 4명의 석학이 강연을 진행한다. 데이터가 중심이 되는 시대를 맞아 국내 디지털유산 분야의 나아갈 방향을 논의하는 두 번째 세션에서는 이코모스* CIPA 명예 위원장이자 이코모스 인터내셔널 사무총장을 역임한 마리오 산타나 퀸테로(Mario Santana Quintero) 캐나다 칼튼대학교 건설환경공학부 교수가 세션 1의 발제자들과 함께 토론을 진행한다. *이코모스(International Council on Monuments and Sites, ICOMOS): 국제기념물유적협의회

이어지는 특별 세션에서는 안재홍 문화기술대학원 교수가 '디지털유산 워킹그룹 설립: 조직 구성 및 운영 방향'을 제안한다. 유정민 한국전통문화대학교 문화유산산업학과 교수, 조영훈 공주대학교 문화재보존과학과 교수, 강동석 동국대학교 고고미술사학과 교수, 강현 국립문화재연구원 건축문화재연구실 연구관이 참여해 국내 디지털유산 분야의 발전을 촉진하기 위한 전문가 네트워킹에 대한 의견과 계획을 공유한다. 둘째 날인 24일은 2025년 CIPA 심포지엄을 위한 교육 프로그램을 중심으로 운영된다. '디지털유산과의 만남'을 주제로 열리는 세션 1에서는 마리오 산타나 퀸테로(Mario Santana Quintero) 교수, 토마스 리고트(Thomas Rigauts) 유네스코 세계유산센터 파리본부 사업운영전문관, 조 칼라스(Joe Kallas) 유네스코 컨설턴트, 미셀 두엉(Michelle Duong) ICOMOS CIPA 집행이사회 이사가 강연한다. 이어, '문화유산과 데이터 및 AI 기술'을 주제로 문화유산 데이터 기반의 AI 음성 도슨트 개발 실습 워크숍이 진행된다. 사전 등록으로 참여한 학부생들이 디지털유산 분야에 대한 이해도를 높일 수 있도록 기획되었으며, 인공지능 교육 전문업체인 스코프랩스(Scopelabs)에서 실습을 맡는다. 다학제적 분야인 디지털유산을 체험할 수 있도록 역사, 문화유산, 공학 등 다양한 전공의 학생들이 팀을 이뤄 수행한다.

이동만 교학부총장은 환영사를 통해 "문화유산 보존을 통해 정체성을 확립하고 후세에 전하기 위한 인류 공동의 미션을 디지털 시대에 부합하게 발전시킬 수 있도록 문화재청과의 협력을 지속해서 강화할 것"이라고 전했다.

이번 심포지엄의 영상은 추후 문화재청을 통해 공개될 예정이며, 심포지엄 웹사이트( https://isdh2023.org/ )에서 관련 자료를 내려받을 수 있다.

문화기술대학원, 제4회 디지털유산 국제심포지엄 개최

우리 대학이 23일(목)부터 이틀간 '제4회 디지털유산 국제심포지엄 개최(The 4th International Symposium on Digital Heritage; ISDH)'을 학술문화관 양승택 오디토리움에서 개최한다.'데이터로서의 문화유산: 유산 보존 관리 및 활용을 위한 디지털 방법론 개발을 선도하는 데이터 중심의 접근 전략'을 주제로 열리는 이번 심포지엄은 문화재청이 주최하고 우리 대학 문화기술대학원이 주관해 디지털헤리티지랩(안재홍, 심혜승)에서 총괄을 맡았다. 특히 이번 행사는 2025년 CIPA 심포지엄*을 우리 대학이 문화재청과 함께 한국에 유치한 것을 기념하기 위해 기획됐다. *CIPA(International Committee of Architectural Photogrammetry) 심포지엄: 1971년 시작되어 현재 2년마다 개최되는 학술대회로, 고고학, 건축학, 보존과학, 디지털 유산 등에서 최신 연구와 기술을 공유하기 위해 다양한 국가와 전문가들이 참여한다. 이를 위해, 디지털유산 분야에서 활발하게 활동하고 있는 국내외 석학 12명이 강연자로 참여한다. 행사 첫날에는 '비전과 미래: 데이터와 문화유산 보존 관리와 활용'을 주제로 한 플레너리 세션과 '데이터로서의 문화유산'을 주제로 한 전문가 토론, 특별 세션이 진행된다.

유럽 타임머신 프로젝트 독일 대사인 샌더 뮨스터(Sander Munster) 독일 프리드리히 실러 예나 대학교 디지털인문학과 교수, 이원재 문화기술대학원 교수, 첸양(Chen Yang) 중국 통지대학교 건축도시계획대학 부교수 겸 호주 퀸즐랜드대학교 건축학부 명예 선임연구원, 유정민 한국전통문화대학교 문화유산산업학과 교수 등 4명의 석학이 강연을 진행한다. 데이터가 중심이 되는 시대를 맞아 국내 디지털유산 분야의 나아갈 방향을 논의하는 두 번째 세션에서는 이코모스* CIPA 명예 위원장이자 이코모스 인터내셔널 사무총장을 역임한 마리오 산타나 퀸테로(Mario Santana Quintero) 캐나다 칼튼대학교 건설환경공학부 교수가 세션 1의 발제자들과 함께 토론을 진행한다. *이코모스(International Council on Monuments and Sites, ICOMOS): 국제기념물유적협의회

이어지는 특별 세션에서는 안재홍 문화기술대학원 교수가 '디지털유산 워킹그룹 설립: 조직 구성 및 운영 방향'을 제안한다. 유정민 한국전통문화대학교 문화유산산업학과 교수, 조영훈 공주대학교 문화재보존과학과 교수, 강동석 동국대학교 고고미술사학과 교수, 강현 국립문화재연구원 건축문화재연구실 연구관이 참여해 국내 디지털유산 분야의 발전을 촉진하기 위한 전문가 네트워킹에 대한 의견과 계획을 공유한다. 둘째 날인 24일은 2025년 CIPA 심포지엄을 위한 교육 프로그램을 중심으로 운영된다. '디지털유산과의 만남'을 주제로 열리는 세션 1에서는 마리오 산타나 퀸테로(Mario Santana Quintero) 교수, 토마스 리고트(Thomas Rigauts) 유네스코 세계유산센터 파리본부 사업운영전문관, 조 칼라스(Joe Kallas) 유네스코 컨설턴트, 미셀 두엉(Michelle Duong) ICOMOS CIPA 집행이사회 이사가 강연한다. 이어, '문화유산과 데이터 및 AI 기술'을 주제로 문화유산 데이터 기반의 AI 음성 도슨트 개발 실습 워크숍이 진행된다. 사전 등록으로 참여한 학부생들이 디지털유산 분야에 대한 이해도를 높일 수 있도록 기획되었으며, 인공지능 교육 전문업체인 스코프랩스(Scopelabs)에서 실습을 맡는다. 다학제적 분야인 디지털유산을 체험할 수 있도록 역사, 문화유산, 공학 등 다양한 전공의 학생들이 팀을 이뤄 수행한다.

이동만 교학부총장은 환영사를 통해 "문화유산 보존을 통해 정체성을 확립하고 후세에 전하기 위한 인류 공동의 미션을 디지털 시대에 부합하게 발전시킬 수 있도록 문화재청과의 협력을 지속해서 강화할 것"이라고 전했다.

이번 심포지엄의 영상은 추후 문화재청을 통해 공개될 예정이며, 심포지엄 웹사이트( https://isdh2023.org/ )에서 관련 자료를 내려받을 수 있다.

2023.11.23

조회수 1399

-

3차원 적층형 화합물 반도체 소자 제작 성공

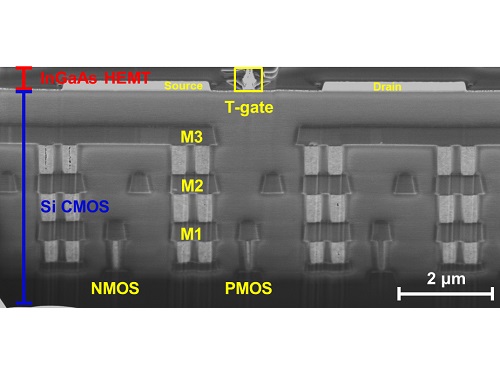

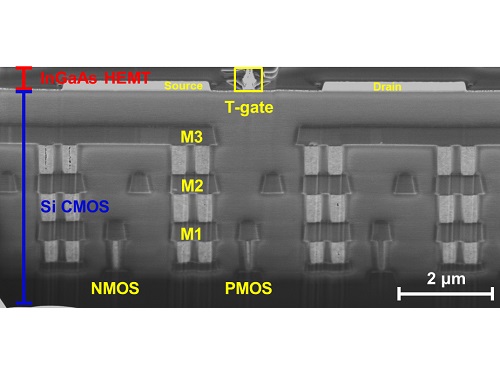

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14

조회수 49219

-

정명수 교수, 테라바이트(TB) 메모리 시대 열어

*비휘발성 메모리(이하 NVDIMM)와 *초저지연 SSD(반도체 저장장치)가 하나의 메모리로 통합돼, 소수의 글로벌 기업만이 주도하고 있는 미래 *영구 메모리(Persistent Memory)보다 성능과 용량이 대폭 향상된 메모리 기술이 우리 연구진에 의해 개발됐다.

☞ 비휘발성 메모리(NVDIMM; Non-Volatile DIMM): 기존 D램(DRAM)에 플래시 메모리와 슈퍼 커패시터를 추가해 정전 때에도 데이터를 유지할 수 있는 메모리.

☞ 초저지연 SSD(Ultra Low Latency SSD): 기존 SSD를 개선해, 매우 낮은 지연시간을 갖는 SSD.

☞ 영구 메모리(Persistent Memory): 데이터의 보존성을 가지는 메모리.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 운영체제 연구실)이 비휘발성 메모리와 초저지연 SSD를 하나의 메모리 공간으로 통합하는 메모리-오버-스토리지(Memory-over-Storage, 이하 MoS) 기술 개발에 성공했다고 16일 밝혔다.

정 교수팀이 새롭게 개발한 이 기술은 기존 스토리지 기술을 재사용하는 데 인텔 옵테인 대비, 메모리 슬롯당 4배 이상인 테라바이트(TB=1,024GB) 수준의 저장 용량을 제공하면서도 휘발성 메모리(D램)과 유사한 사용자 수준의 데이터 처리 속도를 낼 수 있다.

기존 NVDIMM은 운영체제의 도움 없이 CPU가 직접 비휘발성 메모리에 접근할 수 있다는 장점이 있다. 반면 NVDIMM은 D램을 그대로 활용하고 배터리 크기를 무한히 키울 수 없기 때문에 대용량 데이터를 처리할 수 없다는 게 문제다. 이를 해결하기 위한 대안으로는 인텔의 옵테인 메모리 (Intel Optane DC PMM)와 메모리 드라이브 기술(Intel Memory Drive Technology) 등이 있다. 그러나 이러한 기술들은 비휘발성 메모리에 접근할 때마다 운영체제의 도움이 필요해 NVDIMM에 비해 50% 수준으로 읽기/쓰기 속도가 떨어진다.

정 교수팀이 제안한 MoS 기술은 초저지연 SSD를 주 메모리로 활용하고, NVDIMM을 *캐시메모리로 활용한다. 이 결과, SSD 대용량의 저장 공간을 사용자에게 메모리로 사용하게 해줌과 동시에 NVDIMM 단독 사용 시와 유사한 성능을 얻게 함으로써 미래 영구 메모리 기술들이 가지는 한계점을 전면 개선했다.

☞ 캐시: 자주 사용되는 데이터에 빨리 접근할 수 있도록 느린 메모리에 저장된 데이터를 빠른 메모리에 복사해 두는 기법.

MoS 기술은 메인보드나 CPU 내부에 있는 *메모리 컨트롤러 허브(이하 MCH)에 적용돼 사용자의 모든 메모리 요청을 처리한다. 사용자 요청은 일반적으로 NVDIMM 캐시 메모리에서 처리되지만 NVDIMM에 저장되지 않은 데이터의 경우 초저지연 SSD에서 데이터를 읽어와야 한다. 기존 기술들은 운영체제가 이러한 SSD 읽기를 처리하는 반면, 개발된 MoS 기술은 MCH 내부에서 하드웨어가 SSD 입출력을 직접 처리함으로써 초저지연 SSD에 접근 시 발생하는 운영체제(OS)의 입출력 오버헤드(추가로 요구되는 시간)를 완화하는 한편 SSD의 큰 용량을 일반 메모리처럼 사용할 수 있게 해준다.

☞ 메모리 컨트롤러 허브: 일반적으로 노스 브릿지(North Bridge)로 알려져 있으며, CPU가 메모리(DRAM)나 그래픽 처리장치(GPU)와 같은 고대역폭 장치에 접근할 수 있도록 도와주는 하드웨어.

정 교수가 이번에 개발한 MoS 기술은 소프트웨어 기반 메모리 드라이브나 옵테인 영구 메모리 기술 대비 45% 절감된 에너지 소모량으로 110%의 데이터 읽기/쓰기 속도 향상을 달성했다. 결과적으로 대용량의 메모리가 필요하고 정전으로 인한 시스템 장애에 민감한 데이터 센터, 슈퍼컴퓨터 등에 사용되는 기존 메모리/미래 영구 메모리를 대체할 수 있을 것으로 기대된다.

정명수 교수는 "미래 영구 메모리 기술은 일부 해외 유수 기업이 주도하고 있지만, 이번 연구성과를 기반으로 국내 기술과 기존 스토리 및 메모리 기술을 통해 관련 시장에서 우위를 선점할 수 있는 가능성을 열었다는 점에서 의미가 있다"고 강조했다.

이번 연구는 올해 6월에 열릴 컴퓨터 구조 분야 최우수 학술대회인 '이스카(ISCA, International Symposium on Computer Architecture), 2021'에 관련 논문(논문명: Revamping Storage Class Memory With Hardware Automated Memory-Over-Storage Solution)으로 발표될 예정이다. 또 해당 연구에 대한 자세한 내용은 연구실 웹사이트(http://camelab.org)에서 확인할 수 있다.

한편 이번 연구는 과학기술정보통신부와 한국연구재단이 추진하는 우수신진(중견연계) 사업, KAIST 정착연구사업 등의 지원을 받아 수행됐다.

정명수 교수, 테라바이트(TB) 메모리 시대 열어

*비휘발성 메모리(이하 NVDIMM)와 *초저지연 SSD(반도체 저장장치)가 하나의 메모리로 통합돼, 소수의 글로벌 기업만이 주도하고 있는 미래 *영구 메모리(Persistent Memory)보다 성능과 용량이 대폭 향상된 메모리 기술이 우리 연구진에 의해 개발됐다.

☞ 비휘발성 메모리(NVDIMM; Non-Volatile DIMM): 기존 D램(DRAM)에 플래시 메모리와 슈퍼 커패시터를 추가해 정전 때에도 데이터를 유지할 수 있는 메모리.

☞ 초저지연 SSD(Ultra Low Latency SSD): 기존 SSD를 개선해, 매우 낮은 지연시간을 갖는 SSD.

☞ 영구 메모리(Persistent Memory): 데이터의 보존성을 가지는 메모리.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 운영체제 연구실)이 비휘발성 메모리와 초저지연 SSD를 하나의 메모리 공간으로 통합하는 메모리-오버-스토리지(Memory-over-Storage, 이하 MoS) 기술 개발에 성공했다고 16일 밝혔다.

정 교수팀이 새롭게 개발한 이 기술은 기존 스토리지 기술을 재사용하는 데 인텔 옵테인 대비, 메모리 슬롯당 4배 이상인 테라바이트(TB=1,024GB) 수준의 저장 용량을 제공하면서도 휘발성 메모리(D램)과 유사한 사용자 수준의 데이터 처리 속도를 낼 수 있다.

기존 NVDIMM은 운영체제의 도움 없이 CPU가 직접 비휘발성 메모리에 접근할 수 있다는 장점이 있다. 반면 NVDIMM은 D램을 그대로 활용하고 배터리 크기를 무한히 키울 수 없기 때문에 대용량 데이터를 처리할 수 없다는 게 문제다. 이를 해결하기 위한 대안으로는 인텔의 옵테인 메모리 (Intel Optane DC PMM)와 메모리 드라이브 기술(Intel Memory Drive Technology) 등이 있다. 그러나 이러한 기술들은 비휘발성 메모리에 접근할 때마다 운영체제의 도움이 필요해 NVDIMM에 비해 50% 수준으로 읽기/쓰기 속도가 떨어진다.

정 교수팀이 제안한 MoS 기술은 초저지연 SSD를 주 메모리로 활용하고, NVDIMM을 *캐시메모리로 활용한다. 이 결과, SSD 대용량의 저장 공간을 사용자에게 메모리로 사용하게 해줌과 동시에 NVDIMM 단독 사용 시와 유사한 성능을 얻게 함으로써 미래 영구 메모리 기술들이 가지는 한계점을 전면 개선했다.

☞ 캐시: 자주 사용되는 데이터에 빨리 접근할 수 있도록 느린 메모리에 저장된 데이터를 빠른 메모리에 복사해 두는 기법.

MoS 기술은 메인보드나 CPU 내부에 있는 *메모리 컨트롤러 허브(이하 MCH)에 적용돼 사용자의 모든 메모리 요청을 처리한다. 사용자 요청은 일반적으로 NVDIMM 캐시 메모리에서 처리되지만 NVDIMM에 저장되지 않은 데이터의 경우 초저지연 SSD에서 데이터를 읽어와야 한다. 기존 기술들은 운영체제가 이러한 SSD 읽기를 처리하는 반면, 개발된 MoS 기술은 MCH 내부에서 하드웨어가 SSD 입출력을 직접 처리함으로써 초저지연 SSD에 접근 시 발생하는 운영체제(OS)의 입출력 오버헤드(추가로 요구되는 시간)를 완화하는 한편 SSD의 큰 용량을 일반 메모리처럼 사용할 수 있게 해준다.

☞ 메모리 컨트롤러 허브: 일반적으로 노스 브릿지(North Bridge)로 알려져 있으며, CPU가 메모리(DRAM)나 그래픽 처리장치(GPU)와 같은 고대역폭 장치에 접근할 수 있도록 도와주는 하드웨어.

정 교수가 이번에 개발한 MoS 기술은 소프트웨어 기반 메모리 드라이브나 옵테인 영구 메모리 기술 대비 45% 절감된 에너지 소모량으로 110%의 데이터 읽기/쓰기 속도 향상을 달성했다. 결과적으로 대용량의 메모리가 필요하고 정전으로 인한 시스템 장애에 민감한 데이터 센터, 슈퍼컴퓨터 등에 사용되는 기존 메모리/미래 영구 메모리를 대체할 수 있을 것으로 기대된다.

정명수 교수는 "미래 영구 메모리 기술은 일부 해외 유수 기업이 주도하고 있지만, 이번 연구성과를 기반으로 국내 기술과 기존 스토리 및 메모리 기술을 통해 관련 시장에서 우위를 선점할 수 있는 가능성을 열었다는 점에서 의미가 있다"고 강조했다.

이번 연구는 올해 6월에 열릴 컴퓨터 구조 분야 최우수 학술대회인 '이스카(ISCA, International Symposium on Computer Architecture), 2021'에 관련 논문(논문명: Revamping Storage Class Memory With Hardware Automated Memory-Over-Storage Solution)으로 발표될 예정이다. 또 해당 연구에 대한 자세한 내용은 연구실 웹사이트(http://camelab.org)에서 확인할 수 있다.

한편 이번 연구는 과학기술정보통신부와 한국연구재단이 추진하는 우수신진(중견연계) 사업, KAIST 정착연구사업 등의 지원을 받아 수행됐다.

2021.03.16

조회수 98570

-

MOSFET보다 빠른 저전력 트랜지스터 개발

우리 대학 물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동 전력 소모량이 10배 이상 낮고 동작 속도가 2배 이상 빠른 저전력, 고속 터널 트랜지스터를 개발했다. 이제까지 구현된 저전력 트랜지스터 중 MOSFET보다 빠른 트랜지스터의 개발은 최초이다.

조 교수 연구팀은 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 붕화 질소 (hexagonal boron nitride)를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 상태 전류를 높이는데 성공했다. 이제까지의 저전력 트랜지스터는 전력 소모는 낮지만, 작동 상태 전류가 기존 MOSFET에 비해 현저히 작아서 작동 속도가 느린 문제점이 있었다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘나노 레터스 (Nano Letters)’ 4월 24일 자 온라인판에 게재됐다. (논문명 : Monolayer Hexagonal Boron Nitride Tunnel Barrier Contact for Low-Power Black Phosphorus Heterojunction Tunnel Field-Effect Transistors)

트랜지스터의 전력 소모를 감소시키기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 subthreshold swing (SS, 전류를 10배 증가시키는데 필요한 전압값, 단위: mV/decade = mV/dec)을 낮추는 것이 필요한데, 기존의 MOSFET은 thermal carrier injection mechanism 때문에 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다는 한계를 지닌다. band-to-band-tunneling을 carrier injection mechanism으로 가지는 터널 트랜지스터는 상온에서 SS 값이 60 mV/dec 미만으로 낮아질 수 있기 때문에 MOSFET을 대체할 수 있는 저전력 소자로 제안되어왔다. 지난 1월 조교수 연구팀은 흑린을 사용하여 60 mV/dec미만의 SS를 가지는 저전력 트랜지스터를 개발하는데 성공하여 Nature Nanotechnology에 결과를 보고하였다. 하지만, 그 결과 또한 여전히 작동 상태 전류, 특히 SS = 60 mV/dec인 지점에서의 전류가 0.6 μA/μm로 MOSFET의 threshold에서의 전류값 1-10μA/μm보다 낮은 한계가 있었다.

조 교수 연구팀은 본 연구에서 단층 붕화 질소를 활용하여 지난 연구의 한계를 극복하고 SS = 60mV/dec 지점에서의 작동 상태 전류를 Nature Nanotechnology에 보고한 저전력 흑린 트랜지스터에서의 결과보다 10배 이상 크고, MOSFET의 threshold에서의 전류값보다도 큰 20 μA/μm을 달성했다. 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 hexagonal boron nitride를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 속도를 높이는데 성공하여 저전력 고속 트랜지스터의 구성 요건을 완성했다는 점에서 큰 의의가 있다.

조성재 교수는 “흑린 이종접합 트랜지스터가 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동하는 것을 확인했다. 이는 기존 실리콘 기반의 MOSFET을 대체할 수 있는 새로운 트랜지스터의 가능성을 보여주는 결과이다.”라며 “이번 연구 결과를 바탕으로 기초 반도체 물리학 및 비메모리 반도체 산업에 다양한 응용이 가능할 것으로 기대한다.”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

MOSFET보다 빠른 저전력 트랜지스터 개발

우리 대학 물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동 전력 소모량이 10배 이상 낮고 동작 속도가 2배 이상 빠른 저전력, 고속 터널 트랜지스터를 개발했다. 이제까지 구현된 저전력 트랜지스터 중 MOSFET보다 빠른 트랜지스터의 개발은 최초이다.

조 교수 연구팀은 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 붕화 질소 (hexagonal boron nitride)를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 상태 전류를 높이는데 성공했다. 이제까지의 저전력 트랜지스터는 전력 소모는 낮지만, 작동 상태 전류가 기존 MOSFET에 비해 현저히 작아서 작동 속도가 느린 문제점이 있었다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘나노 레터스 (Nano Letters)’ 4월 24일 자 온라인판에 게재됐다. (논문명 : Monolayer Hexagonal Boron Nitride Tunnel Barrier Contact for Low-Power Black Phosphorus Heterojunction Tunnel Field-Effect Transistors)

트랜지스터의 전력 소모를 감소시키기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 subthreshold swing (SS, 전류를 10배 증가시키는데 필요한 전압값, 단위: mV/decade = mV/dec)을 낮추는 것이 필요한데, 기존의 MOSFET은 thermal carrier injection mechanism 때문에 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다는 한계를 지닌다. band-to-band-tunneling을 carrier injection mechanism으로 가지는 터널 트랜지스터는 상온에서 SS 값이 60 mV/dec 미만으로 낮아질 수 있기 때문에 MOSFET을 대체할 수 있는 저전력 소자로 제안되어왔다. 지난 1월 조교수 연구팀은 흑린을 사용하여 60 mV/dec미만의 SS를 가지는 저전력 트랜지스터를 개발하는데 성공하여 Nature Nanotechnology에 결과를 보고하였다. 하지만, 그 결과 또한 여전히 작동 상태 전류, 특히 SS = 60 mV/dec인 지점에서의 전류가 0.6 μA/μm로 MOSFET의 threshold에서의 전류값 1-10μA/μm보다 낮은 한계가 있었다.

조 교수 연구팀은 본 연구에서 단층 붕화 질소를 활용하여 지난 연구의 한계를 극복하고 SS = 60mV/dec 지점에서의 작동 상태 전류를 Nature Nanotechnology에 보고한 저전력 흑린 트랜지스터에서의 결과보다 10배 이상 크고, MOSFET의 threshold에서의 전류값보다도 큰 20 μA/μm을 달성했다. 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 hexagonal boron nitride를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 속도를 높이는데 성공하여 저전력 고속 트랜지스터의 구성 요건을 완성했다는 점에서 큰 의의가 있다.

조성재 교수는 “흑린 이종접합 트랜지스터가 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동하는 것을 확인했다. 이는 기존 실리콘 기반의 MOSFET을 대체할 수 있는 새로운 트랜지스터의 가능성을 보여주는 결과이다.”라며 “이번 연구 결과를 바탕으로 기초 반도체 물리학 및 비메모리 반도체 산업에 다양한 응용이 가능할 것으로 기대한다.”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

2020.05.06

조회수 10679

-

저전력·고속 터널 전계효과 트랜지스터 개발

물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동전력 소모량이 10배 이상, 대기전력 소모량이 1만 배 가까이 적은 저전력, 고속 트랜지스터를 개발했다.

조 교수 연구팀은 2차원 물질인 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 두 물질의 접합이 아닌 단일 물질의 두께 차이에 의한 이종접합 터널을 제작하는 데 성공했다. 이러한 단일 물질의 이종접합을 터널 트랜지스터에 활용하면 서로 다른 물질로 제작한 이종접합 트랜지스터에서 발생했던 격자 불균형, 결함, 계면 산화 등의 문제를 해결할 수 있어 고성능 터널 트랜지스터의 개발이 가능하다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘네이처 나노테크놀로지 (Nature Nanotechnology)’ 1월 27일 자 온라인판에 게재됐다. (논문명 : Thickness-controlled black phosphorus tunnel field-effect transistor fro low-power switches).

무어 법칙에 따른 트랜지스터 소형화 및 집적도 증가는 현대의 정보화 기술을 가능하게 했지만 최근 트랜지스터의 소형화가 양자역학적 한계에 다다르면서 전력 소모가 급격히 증가해 이제는 무어 법칙에 따라 트랜지스터 소형화가 진행되지 못하는 상황이다. 최근에는 자율주행차, 사물인터넷 등의 등장으로 많은 양의 데이터를 저전력, 고속으로 처리할 수 있는 비메모리 반도체의 기술 발달이 시급히 요구되고 있다.

트랜지스터의 전력 소모는 크게 작동 전력 소모와 대기 전력 소모로 나뉜다. 작동 전력과 대기 전력을 같이 낮추기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 전류를 10배 증가시키는데 필요한 전압으로 정의되는 SS 값(subthreshold swing, 단위: mV/decade = mV/dec)의 감소가 필요한데, 금속 산화물 반도체 전계효과 트랜지스터에서는 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다. 이를 해결하기 위해서는 상온에서 SS 값을 60 mV/dec 이하로 낮출 수 있는 새로운 트랜지스터의 개발이 필요하다. 이전에 개발되었던 낮은 SS를 가지는 저전력 터널 트랜지스터의 경우 트랜지스터 채널을 구성하는 두 물질의 이종접합 계면에서 산화막 등의 문제가 발생하여 작동 상태에서 낮은 전류를 가지는 문제가 있었다. 작동 상태 전류는 트랜지스터 작동속도에 비례하기 때문에, 낮은 작동 상태 전류는 저전력 트랜지스터의 경쟁력을 떨어뜨린다.

조 교수 연구팀이 적은 전력소모를 위한 낮은 SS 값과 고속 작동을 위한 높은 작동 상태 전류를 단일 트랜지스터에서 동시에 달성한 것은 유례없는 일로 2차원 물질 기반의 저전력 트랜지스터가 기존의 금속 산화물 반도체 전계효과 트랜지스터의 전력 소모 문제를 해결하고, 궁극적으로 기존 트랜지스터를 대체하고 미래의 저전력 대체 트랜지스터가 될 수 있음을 의미한다. 조성재 교수는 “이번 연구는 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동해 실리콘 기반의 CMOS 트랜지스터를 대체할 수 있는 저전력 소자의 필요충분조건을 최초로 만족시킨 개발이다”라며 “대한민국 비메모리 산업뿐 아니라 세계적으로 기초 반도체 물리학 및 산업 응용에 큰 의의를 지닌다”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

저전력·고속 터널 전계효과 트랜지스터 개발

물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동전력 소모량이 10배 이상, 대기전력 소모량이 1만 배 가까이 적은 저전력, 고속 트랜지스터를 개발했다.

조 교수 연구팀은 2차원 물질인 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 두 물질의 접합이 아닌 단일 물질의 두께 차이에 의한 이종접합 터널을 제작하는 데 성공했다. 이러한 단일 물질의 이종접합을 터널 트랜지스터에 활용하면 서로 다른 물질로 제작한 이종접합 트랜지스터에서 발생했던 격자 불균형, 결함, 계면 산화 등의 문제를 해결할 수 있어 고성능 터널 트랜지스터의 개발이 가능하다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘네이처 나노테크놀로지 (Nature Nanotechnology)’ 1월 27일 자 온라인판에 게재됐다. (논문명 : Thickness-controlled black phosphorus tunnel field-effect transistor fro low-power switches).

무어 법칙에 따른 트랜지스터 소형화 및 집적도 증가는 현대의 정보화 기술을 가능하게 했지만 최근 트랜지스터의 소형화가 양자역학적 한계에 다다르면서 전력 소모가 급격히 증가해 이제는 무어 법칙에 따라 트랜지스터 소형화가 진행되지 못하는 상황이다. 최근에는 자율주행차, 사물인터넷 등의 등장으로 많은 양의 데이터를 저전력, 고속으로 처리할 수 있는 비메모리 반도체의 기술 발달이 시급히 요구되고 있다.

트랜지스터의 전력 소모는 크게 작동 전력 소모와 대기 전력 소모로 나뉜다. 작동 전력과 대기 전력을 같이 낮추기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 전류를 10배 증가시키는데 필요한 전압으로 정의되는 SS 값(subthreshold swing, 단위: mV/decade = mV/dec)의 감소가 필요한데, 금속 산화물 반도체 전계효과 트랜지스터에서는 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다. 이를 해결하기 위해서는 상온에서 SS 값을 60 mV/dec 이하로 낮출 수 있는 새로운 트랜지스터의 개발이 필요하다. 이전에 개발되었던 낮은 SS를 가지는 저전력 터널 트랜지스터의 경우 트랜지스터 채널을 구성하는 두 물질의 이종접합 계면에서 산화막 등의 문제가 발생하여 작동 상태에서 낮은 전류를 가지는 문제가 있었다. 작동 상태 전류는 트랜지스터 작동속도에 비례하기 때문에, 낮은 작동 상태 전류는 저전력 트랜지스터의 경쟁력을 떨어뜨린다.

조 교수 연구팀이 적은 전력소모를 위한 낮은 SS 값과 고속 작동을 위한 높은 작동 상태 전류를 단일 트랜지스터에서 동시에 달성한 것은 유례없는 일로 2차원 물질 기반의 저전력 트랜지스터가 기존의 금속 산화물 반도체 전계효과 트랜지스터의 전력 소모 문제를 해결하고, 궁극적으로 기존 트랜지스터를 대체하고 미래의 저전력 대체 트랜지스터가 될 수 있음을 의미한다. 조성재 교수는 “이번 연구는 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동해 실리콘 기반의 CMOS 트랜지스터를 대체할 수 있는 저전력 소자의 필요충분조건을 최초로 만족시킨 개발이다”라며 “대한민국 비메모리 산업뿐 아니라 세계적으로 기초 반도체 물리학 및 산업 응용에 큰 의의를 지닌다”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

2020.02.20

조회수 12893

-

KAIST, 2년 연속 아시아 최고 혁신대학 1위 선정

우리대학이 2017년 ‘로이터 랭킹-아시아 최고 혁신대학 75(Reuters Top 75: Asia’s Most Innovative Universities)' 순위에서 작년에 이어 올해에도 2년 연속 1위를 차지했다.

로이터는 클래리베이트 애널리틱스(Clarivate Analytics)와 공동으로 2010년부터 2015년까지 아시아 각 대학의 학술논문 및 특허출원 실적 등을 종합 분석해 2017년 아시아에서 가장 혁신적인 교육기관 상위 75개 대학의 순위를 매긴 후 그 결과를 8일 공개했다. 평가지표는 특허출원 수, 특허성공률, 국제특허, 특허인용 수, 특허인용 비율, 특허인용 논문 영향력, 산업계논문인용 영향력 등 10개다. 로이터는 이들 10개 지표를 모두 고려해 평가에 종합 반영함으로써 75개 대학의 순위를 결정한다.

올해로 2회째를 맞이한 이번 조사에서 우리대학은 아시아 최고 혁신대학으로 작년에 이어 2년 연속 1위를 차지했다. 우리대학은 로이터통신이 2009~2014년 자료를 기초로 산정한 2016년 혁신대학 순위에서 아시아 대학 중 1위를, 세계대학 중 6위를 각각 기록했다. 우리대학은 올해 평가에서 “2010년부터 2015년까지 923개의 특허를 신청해 75개 상위 교육기관 중 가장 많은 수의 특허를 출원했고 특허 성공률뿐만 아니라 외부 연구자들이 KAIST의 특허를 연구논문과 특허에 자주 인용했기 때문에 높은 점수를 받았다”고 로이터측은 밝혔다.

로이터가 8일 발표한 자료에 따르면 우리나라는 상위 5위 안에 우리대학을 포함한 4개의 대학이, 상위 20위 안에는 8개 대학을 배출하는 등 총 22개 대학이 상위 75개 대학 명단에 포함됐다. 홍콩을 포함한 중국이 25개로 1위를 차지했고 일본이 19개로 우리나라의 뒤를 이었다.

이밖에 호주(5개), 싱가포르(2개), 뉴질랜드(1개)와 인도(1개) 대학 순으로 조사됐다. 2017년 상위 20위권 안에 포함된 국내 대학은 △KAIST(1위) △서울대(2위) △포스텍(4위) △성균관대(5위) △한양대(10위) △연세대(14위) △고려대(15위) △GIST(광주과학기술원, 18위) 순이다.

한편 김진우 클래리베이트 애널리틱스 한국지사장은 오는 15일 오후 KAIST를 방문해 신성철 총장에게 우리대학이 ‘로이터 Top 75: 아시아 최고 혁신대학 2017’ 조사에서 1위로 선정된 내용을 담은 기념패를 전달할 예정이다.

KAIST, 2년 연속 아시아 최고 혁신대학 1위 선정

우리대학이 2017년 ‘로이터 랭킹-아시아 최고 혁신대학 75(Reuters Top 75: Asia’s Most Innovative Universities)' 순위에서 작년에 이어 올해에도 2년 연속 1위를 차지했다.

로이터는 클래리베이트 애널리틱스(Clarivate Analytics)와 공동으로 2010년부터 2015년까지 아시아 각 대학의 학술논문 및 특허출원 실적 등을 종합 분석해 2017년 아시아에서 가장 혁신적인 교육기관 상위 75개 대학의 순위를 매긴 후 그 결과를 8일 공개했다. 평가지표는 특허출원 수, 특허성공률, 국제특허, 특허인용 수, 특허인용 비율, 특허인용 논문 영향력, 산업계논문인용 영향력 등 10개다. 로이터는 이들 10개 지표를 모두 고려해 평가에 종합 반영함으로써 75개 대학의 순위를 결정한다.

올해로 2회째를 맞이한 이번 조사에서 우리대학은 아시아 최고 혁신대학으로 작년에 이어 2년 연속 1위를 차지했다. 우리대학은 로이터통신이 2009~2014년 자료를 기초로 산정한 2016년 혁신대학 순위에서 아시아 대학 중 1위를, 세계대학 중 6위를 각각 기록했다. 우리대학은 올해 평가에서 “2010년부터 2015년까지 923개의 특허를 신청해 75개 상위 교육기관 중 가장 많은 수의 특허를 출원했고 특허 성공률뿐만 아니라 외부 연구자들이 KAIST의 특허를 연구논문과 특허에 자주 인용했기 때문에 높은 점수를 받았다”고 로이터측은 밝혔다.

로이터가 8일 발표한 자료에 따르면 우리나라는 상위 5위 안에 우리대학을 포함한 4개의 대학이, 상위 20위 안에는 8개 대학을 배출하는 등 총 22개 대학이 상위 75개 대학 명단에 포함됐다. 홍콩을 포함한 중국이 25개로 1위를 차지했고 일본이 19개로 우리나라의 뒤를 이었다.

이밖에 호주(5개), 싱가포르(2개), 뉴질랜드(1개)와 인도(1개) 대학 순으로 조사됐다. 2017년 상위 20위권 안에 포함된 국내 대학은 △KAIST(1위) △서울대(2위) △포스텍(4위) △성균관대(5위) △한양대(10위) △연세대(14위) △고려대(15위) △GIST(광주과학기술원, 18위) 순이다.

한편 김진우 클래리베이트 애널리틱스 한국지사장은 오는 15일 오후 KAIST를 방문해 신성철 총장에게 우리대학이 ‘로이터 Top 75: 아시아 최고 혁신대학 2017’ 조사에서 1위로 선정된 내용을 담은 기념패를 전달할 예정이다.

2017.06.09

조회수 11012

-

2017년 총장 신년사

친애하는 KAIST 가족 여러분,

2017년 정유년(丁酉年) 새해가 밝았습니다. 새해 복 많이 받으시고, 댁내 건강과 행복이 가득하기를 기원합니다. 새해에도 여러분의 꿈이 이루어지고, 국민들로부터 큰 사랑과 믿음을 받고 있는 우리 KAIST가 그 성원에 보답할 수 있는 한해가 되기를 바랍니다.

2013년 총장으로 부임하며 Quantum Jump 전략을 수립하고, 전반기(2013~14)에는 ‘하나된 KAIST’를 만들어 구성원의 역량을 결집하고 후반기(2015~16)에는 ‘질적성장을 통해 혁신하는 KAIST’를 만들어 크게 도약하고자 노력했습니다. 지난 4년간 우리는 성장통을 지혜롭게 극복하며 눈부신 발전을 거듭했고, 명실상부한 ‘Students-Centered, Faculty-Driven, World’s Most Innovative Research University’로 발돋움 했습니다.

우리학교의 수월성을 달성하기 위한 ‘창의’와 ‘도전’은 국가발전의 원동력이 되어 왔습니다. 교육·연구·시스템의 지속적인 혁신, 창업문화의 확산, 대학의 사회적 책무를 다하고자 하는 노력들은 학교의 질적성장을 이끌어 왔습니다.

KAIST의 교육은 끊임없이 발전하고 있습니다. 세계적인 대학의 위상에 걸맞는 교육시스템을 마련하고자 세차례에 걸친 고강도 학사조직개편 끝에 미래지향적인 교육 플랫폼이 완성되었습니다. KAIST의 교육은 넓은 학문단위의 학사교육과 융합전공의 대학원교육이 효율적으로 운영될 수 있는 체제에 더하여 학문적 수월성과 창의성이 조화를 이루는 융합형 교육시스템입니다. 우리 학생들은 이러한 π(파이)형 교육시스템 속에서 학사과정간 학문적 기반의 공통점을 바탕으로 기초를 튼튼히 하고, 석‧박사 교육과정간 융합 전공교육과 연구를 통해 지혜와 지식을 체득하고 졸업 후 사회에 진출했을 때 대체불가능한 우수한 인재로 성장하고 있습니다.

새로 도입된 융합 Capstone Design 교과과정은 국내 공학교육의 패러다임을 현장중심형 교육으로 새롭게 바꾸는 계기를 마련했습니다. 본 과정을 통해 우리 학생들은 사회가 필요로 하는 과제를 직접 기획하고 도출된 문제를 해결해 봄으로써 창의성, 실무능력, 팀워크 및 리더십을 갖추게 될 것입니다.

우리학교는 Education 3.0을 통해 수요자 중심의 교육시스템을 선도하고 있습니다. 학생들은 강의 전에 제공받은 온라인 콘텐츠로 자기주도 사전학습을 수행하고, 수업시간에는 지식전달식 강의 대신 배움의 주체가 되어 팀원들과 협력학습을 하며 전공지식과 문제해결 및 소통능력 등을 체득하게 됩니다. 우리학교는 자체적으로 개발한 온라인 공개강좌 서비스인 KOOC(KAIST MOOC)을 개방함으로써 KAIST의 우수한 교육을 국내‧외에 무상으로 제공하며 대학의 사회적 책무를 다하고 있습니다.

KAIST의 연구역량은 세계적인 대학들과 어깨를 나란히 하고 있습니다. 우리학교의 혁신적인 교육 및 연구역량은 이미 QS, THE 등 세계 유수의 기관들로부터 널리 인정받고 있으며, 로이터통신은 매년 세계가 놀랄만한 연구성과를 발표하고 있는 우리학교를 ‘세계 혁신대학 6위’로 선정한바 있습니다. KAIST가 지금과 같이 지속적으로 발전하기 위해서는 단기적인 소나기 정책에 의한 연구보다는 늘 한 곳에서 샘솟는 샘물같이 지속가능한 연구를 수행할 수 있어야 합니다. 특히, 인류발전에 공헌할 수 있는 아이디어가 지속적으로 창출되고, 그 연구를 안정적으로 뒷받침 할 수 있는 재원이 마련되어야 하며, 누구나 꿈을 가지고 도전하며 도전의 성공여부 보다는 그 도전의 성실성이 평가되는 연구문화가 구축되어야 할 것입니다. KAIST 그랜드챌린지30 프로젝트와 같이 선도적인 연구지원제도를 신설한 것도 우리 KAIST가 앞장서서 인류가 당면한 거대한 문제들을 해결하고, 혁신적인 연구문화를 확산시키기 위함입니다.

생명과학분야의 글로벌 경쟁력을 확보하기 위해 그동안 KAIST 융합의과학대학원(세종)을 설립하기 위해 노력해왔습니다. 수년간 추진하였던 「KAIST 융합의과학대학원(세종) 설립사업」 예비타당성조사가 많은 분들의 노력으로 조만간 긍정적인 결과를 얻어 2018년부터 정부예산이 반영될 것으로 기대합니다. 우리학교는 융합의과학대학원을 시작으로 세종시에 KAIST의 혁신적인 교육·연구시스템을 구축하게 될 것이고, 융합생명과학분야의 경쟁력있는 교육‧연구역량을 갖추게 될 것입니다.

우리학교는 그동안 우리나라 대학사회의 창업문화를 선도하고 확산하는데 최선을 다해왔습니다. 학생들이 기업가정신을 함양할 수 있는 기회를 널리 제공하고 교원들의 창업활동을 장려함으로써 KAIST의 우수한 교육과 혁신적인 연구성과가 경제적‧사회적 가치로 연결될 수 있도록 노력했습니다. 과학기술 분야의 우수한 인재들이 창업인재로 성장할 수 있도록 지원하는 전담조직인 KAIST 창업원(Institute for Startup KAIST)을 설치하여 창의적인 아이디어가 사업화에 이르는 전 과정을 지원하고 있습니다. 또한 K-School을 설립하여 다양한 학과가 공동으로 운영하는 창업맞춤형 교육프로그램인 창업융합전문석사 과정을 운영하고 있습니다. 그 외에도 창업원 판교센터, KAIST 사회적기업가 MBA(SEMBA) 등 우리학교는 창업과 관련한 다양한 프로그램을 설치‧운영하며 캠퍼스 내 창업분위기를 조성하는 것은 물론 KAIST가 주축이 되어 전국적으로 창업문화가 확산될 수 있도록 노력한 결과 국내대학 창업지수 1위로 선정되는 등 가시적인 성과를 거두고 있습니다.

KAIST의 시스템 혁신은 항상 국내외의 여러 기관으로부터 주목을 받았습니다. 국내 대학 최초로 도입된 테뉴어제도는 세부적인 보완을 통해 정착단계에 접어들었으며, 영어강의와 성적연계 등록금 제도 등은 구성원들의 적극적인 의견수렴과 전문가그룹의 심도있는 검토를 통해 보완‧발전되었습니다.

2013년 심도있는 경영진단을 바탕으로 행정조직의 대대적인 개편이 있었습니다. 기능통합과 의사결정 체계의 간소화를 목표로 단행된 행정조직개편은 KAIST 행정을 ‘변화에 유연히 대응하는 전략적 조직’, ‘핵심기능 중심의 효율적인 조직’, ‘적절하고 명확하게 역할이 부여된 합리적인 조직’, ‘고객지향적인 고객친화적 조직’으로 변화시켰습니다. 또한, 행정발전교육센터를 신설하여 적극투자함으로써 행정분야에서 근무하는 직원들이 지속적으로 자기계발을 할 수 있도록 장려하고, 행정업무에 실질적으로 도움을 줄 수 있는 강좌를 개설하여 행정역량을 제고함으로써 행정서비스의 질을 향상할 수 있도록 했습니다.

구성원들간 원활한 소통이 이루어질 수 있도록 다양한 채널을 설치하고 의견을 청취하는데 많은 노력을 기울였습니다. 우리나라 대학 최초로 총장자문기구로 옴부즈퍼슨 제도를 도입하여 학내에서 발생하는 다양한 고충을 청취하고 중재하였고, 고객만족센터를 설치하여 구성원에게 제공되는 학교서비스의 질을 제고하였으며, 인권윤리센터를 신설하여 인권‧윤리 침해 예방 및 신속한 피해구제를 통해 구성원의 인권을 보호하고 평등하고 다양성이 존중되는 캠퍼스 문화를 조성하였습니다. 총장과 학교 구성원간의 소통은 특정한 시간이나 특별한 기회를 만들어 하는 것이 아니라 상시 자연스럽게 이루어져야 합니다. 총장실 개방, 찾아가는 커피아워, 학부 및 대학원생 초청 간담회, 구성원과의 이메일 교환 등을 통해 여러분의 작은 목소리에도 귀를 기울이려고 적극적으로 노력했고, 교내를 오가며 우연히 만나 나눈 대화들 또한 학교를 운영하는데 큰 도움이 되었습니다.

우리학교는 대전시민들로부터 큰 사랑과 관심을 받고 있습니다. 대전광역시청, 유성구청, 충남대학교 등 지역의 여러 기관들과 긴밀히 소통하며 더불어 사는 길을 마련하고자 노력했습니다. 그 결과, 충남대학교와 우리학교 사이에 위치한 담을 허물고 열린길을 만들었고, 카이스트교를 개통하여 대전시민들에게 한발짝 더 다가가는 계기를 마련하였습니다. 한마음봉사단, 학생들의 김장봉사, 지역의 소외계층을 위한 교육봉사 등을 통해 KAIST가 먼저 지역사회에 다가가는 활동을 장려하고 지원하였으며 이러한 활동은 앞으로도 적극적으로 활성화되어야 할 것입니다.

지난 4년간 지속적인 인프라 개선사업을 추진하여 세계적인 대학의 명성에 걸맞는 교육과 연구를 지원하고 양질의 생활환경을 제공할 수 있는 인프라가 구축되었습니다. 현재 정문술 2관 신축공사가 마무리 되었고, 학술문화창의관 신축과 중앙도서관 리모델링 사업이 진행 중입니다. 우리 캠퍼스는 Startup KAIST Studio 2 신축, 의학연구동(약국) 신축, International Village C동 리모델링, 반도체동(새늘동) 리모델링, 대강당 리모델링, 기계공학동 리모델링, Startup Village 리모델링, 서울캠퍼스 해정사와 8‧9호관 리모델링, 노천극장 리모델링, 화암기숙사 리모델링(예정), 에코 캠퍼스 구축(소나무 이식 등), 안전한 캠퍼스 구축(도로 및 보행자도로 개선 등) 등 신축공사와 노후건물 및 시설의 보수공사 등으로 빠르게 변화하였습니다. 인프라 확충사업 외에도, 문지캠퍼스에 IBS 사업단, 녹색교통대학원 등을 이전하여 기존 스페이스를 효율적으로 사용할 수 있는 방안에 대해 다양한 논의가 진행되고 있습니다.

국제화를 추구하고 다양성을 존중하는 문화는 앞으로 우리학교가 지속적으로 발전하는 원동력이 될 것입니다. 그동안 외국인 교원 10%, 외국인 학생 10%, 여성 교원 10%를 목표로 삼고 우수한 인재를 유치하기 위해 최선을 다한 결과 이제는 10:10:10 이니셔티브(Initiative)를 20:20:20 이니셔티브(Initiative)로 그 목표를 수정할 단계에 이르렀습니다. 나눔관 공동 Kitchen 환경개선, 교내 PODCAST를 통한 외국인 구성원들과의 소통, 할랄푸드 카페테리아(Hallal Food Cafeteria) 오픈, Bilingual 캠퍼스 구축사업, 해외 유수대학들과의 공동학위 프로그램 개설, 해외 인턴십 프로그램 확충, 젠더평등을 위한 제도개선, 여성휴게실 및 육아시설 개선 등 지금까지 우리가 기울였던 노력은 앞으로도 반드시 지속되어야 할 것입니다.

KAIST에 대한 국내외적 관심은 앞으로 더욱 커질 것으로 생각됩니다. 최근 4년간의 학부 지원자 경쟁률 추이가 가파르게 상승하고 있으며, 매우 우수한 학생들이 매년 입학하고 있습니다. 새내기는 물론 재학생들의 학교생활 만족도 또한 지속적으로 향상되면서 학생들의 학교에 대한 관심과 사랑으로 이어지고 있습니다. 최근 재학생, 동문, 학부모 등 우리학교와 직접적으로 관계된 분들의 기부가 급격히 늘어나는 새로운 기부문화가 형성되었고, 지난 4년간 기부건수는 2만 6천여건에 이르며 기부금 총액은 708억여원에 달합니다.국내외의 유수 기관에서 KAIST를 벤치마킹하기 위해 많은 분들이 찾아오고 있고, 몇몇 국가에서는 KAIST 분교를 자국에 설치해 달라는 요청을 한바 있습니다. 이러한 변화는 Happy Campus를 만들기 위한 우리 구성원들의 부단한 노력의 결과라고 생각합니다.

사랑하는 KAIST 가족 여러분,

2017년 신년사는 제가 KAIST 총장으로서 여러분께 드리는 마지막 신년사 입니다. 이사회에서 신임 총장 선임절차가 진행중이며, 2017년 2월 23일 이취임식을 끝으로 저는 여러분과 함께 했던 4년간의 KAIST 생활을 마치고 정들었던 교정을 떠납니다.

KAIST 총장으로서 제게 허락하는 시간까지 단 한 명의 구성원이라도 소외되지 않고 Happy Campus에서 꿈을 펼칠 수 있도록 최선을 다해 노력하겠습니다. 여러분과 함께 했던 지난 4년은 제게 큰 행복이자 영광이었습니다. KAIST를 세계 최고의 대학으로 성장시키고 해피 캠퍼스를 구축하기 위해 각자의 분야에서 헌신해 준 KAIST 전체 가족 여러분께 진심으로 감사드립니다.

여러분은 KAIST의 미래이자 대한민국을 이끌어가는 원동력입니다. 그동안 일구어낸 성과를 바탕으로 각자의 위치에서 인류와 국가의 발전에 공헌 할 수 있는 더욱 큰 꿈을 꾸고 그 꿈을 이루기 위해 최선을 다해주시길 바랍니다.

2017년은 우리 KAIST 가족 여러분의 모든 꿈이 실현되는 희망찬 한 해가 되기를 기원합니다. ‘제4차 산업혁명의 허브(hub)’이자 ‘Students-Centered, Faculty-Driven World’s Best Research University’를 향한 여러분의 도전을 응원합니다.

감사합니다.

2017년 1월 1일

KAIST 총장 강성모

2017년 총장 신년사

친애하는 KAIST 가족 여러분,

2017년 정유년(丁酉年) 새해가 밝았습니다. 새해 복 많이 받으시고, 댁내 건강과 행복이 가득하기를 기원합니다. 새해에도 여러분의 꿈이 이루어지고, 국민들로부터 큰 사랑과 믿음을 받고 있는 우리 KAIST가 그 성원에 보답할 수 있는 한해가 되기를 바랍니다.

2013년 총장으로 부임하며 Quantum Jump 전략을 수립하고, 전반기(2013~14)에는 ‘하나된 KAIST’를 만들어 구성원의 역량을 결집하고 후반기(2015~16)에는 ‘질적성장을 통해 혁신하는 KAIST’를 만들어 크게 도약하고자 노력했습니다. 지난 4년간 우리는 성장통을 지혜롭게 극복하며 눈부신 발전을 거듭했고, 명실상부한 ‘Students-Centered, Faculty-Driven, World’s Most Innovative Research University’로 발돋움 했습니다.

우리학교의 수월성을 달성하기 위한 ‘창의’와 ‘도전’은 국가발전의 원동력이 되어 왔습니다. 교육·연구·시스템의 지속적인 혁신, 창업문화의 확산, 대학의 사회적 책무를 다하고자 하는 노력들은 학교의 질적성장을 이끌어 왔습니다.

KAIST의 교육은 끊임없이 발전하고 있습니다. 세계적인 대학의 위상에 걸맞는 교육시스템을 마련하고자 세차례에 걸친 고강도 학사조직개편 끝에 미래지향적인 교육 플랫폼이 완성되었습니다. KAIST의 교육은 넓은 학문단위의 학사교육과 융합전공의 대학원교육이 효율적으로 운영될 수 있는 체제에 더하여 학문적 수월성과 창의성이 조화를 이루는 융합형 교육시스템입니다. 우리 학생들은 이러한 π(파이)형 교육시스템 속에서 학사과정간 학문적 기반의 공통점을 바탕으로 기초를 튼튼히 하고, 석‧박사 교육과정간 융합 전공교육과 연구를 통해 지혜와 지식을 체득하고 졸업 후 사회에 진출했을 때 대체불가능한 우수한 인재로 성장하고 있습니다.

새로 도입된 융합 Capstone Design 교과과정은 국내 공학교육의 패러다임을 현장중심형 교육으로 새롭게 바꾸는 계기를 마련했습니다. 본 과정을 통해 우리 학생들은 사회가 필요로 하는 과제를 직접 기획하고 도출된 문제를 해결해 봄으로써 창의성, 실무능력, 팀워크 및 리더십을 갖추게 될 것입니다.

우리학교는 Education 3.0을 통해 수요자 중심의 교육시스템을 선도하고 있습니다. 학생들은 강의 전에 제공받은 온라인 콘텐츠로 자기주도 사전학습을 수행하고, 수업시간에는 지식전달식 강의 대신 배움의 주체가 되어 팀원들과 협력학습을 하며 전공지식과 문제해결 및 소통능력 등을 체득하게 됩니다. 우리학교는 자체적으로 개발한 온라인 공개강좌 서비스인 KOOC(KAIST MOOC)을 개방함으로써 KAIST의 우수한 교육을 국내‧외에 무상으로 제공하며 대학의 사회적 책무를 다하고 있습니다.

KAIST의 연구역량은 세계적인 대학들과 어깨를 나란히 하고 있습니다. 우리학교의 혁신적인 교육 및 연구역량은 이미 QS, THE 등 세계 유수의 기관들로부터 널리 인정받고 있으며, 로이터통신은 매년 세계가 놀랄만한 연구성과를 발표하고 있는 우리학교를 ‘세계 혁신대학 6위’로 선정한바 있습니다. KAIST가 지금과 같이 지속적으로 발전하기 위해서는 단기적인 소나기 정책에 의한 연구보다는 늘 한 곳에서 샘솟는 샘물같이 지속가능한 연구를 수행할 수 있어야 합니다. 특히, 인류발전에 공헌할 수 있는 아이디어가 지속적으로 창출되고, 그 연구를 안정적으로 뒷받침 할 수 있는 재원이 마련되어야 하며, 누구나 꿈을 가지고 도전하며 도전의 성공여부 보다는 그 도전의 성실성이 평가되는 연구문화가 구축되어야 할 것입니다. KAIST 그랜드챌린지30 프로젝트와 같이 선도적인 연구지원제도를 신설한 것도 우리 KAIST가 앞장서서 인류가 당면한 거대한 문제들을 해결하고, 혁신적인 연구문화를 확산시키기 위함입니다.

생명과학분야의 글로벌 경쟁력을 확보하기 위해 그동안 KAIST 융합의과학대학원(세종)을 설립하기 위해 노력해왔습니다. 수년간 추진하였던 「KAIST 융합의과학대학원(세종) 설립사업」 예비타당성조사가 많은 분들의 노력으로 조만간 긍정적인 결과를 얻어 2018년부터 정부예산이 반영될 것으로 기대합니다. 우리학교는 융합의과학대학원을 시작으로 세종시에 KAIST의 혁신적인 교육·연구시스템을 구축하게 될 것이고, 융합생명과학분야의 경쟁력있는 교육‧연구역량을 갖추게 될 것입니다.

우리학교는 그동안 우리나라 대학사회의 창업문화를 선도하고 확산하는데 최선을 다해왔습니다. 학생들이 기업가정신을 함양할 수 있는 기회를 널리 제공하고 교원들의 창업활동을 장려함으로써 KAIST의 우수한 교육과 혁신적인 연구성과가 경제적‧사회적 가치로 연결될 수 있도록 노력했습니다. 과학기술 분야의 우수한 인재들이 창업인재로 성장할 수 있도록 지원하는 전담조직인 KAIST 창업원(Institute for Startup KAIST)을 설치하여 창의적인 아이디어가 사업화에 이르는 전 과정을 지원하고 있습니다. 또한 K-School을 설립하여 다양한 학과가 공동으로 운영하는 창업맞춤형 교육프로그램인 창업융합전문석사 과정을 운영하고 있습니다. 그 외에도 창업원 판교센터, KAIST 사회적기업가 MBA(SEMBA) 등 우리학교는 창업과 관련한 다양한 프로그램을 설치‧운영하며 캠퍼스 내 창업분위기를 조성하는 것은 물론 KAIST가 주축이 되어 전국적으로 창업문화가 확산될 수 있도록 노력한 결과 국내대학 창업지수 1위로 선정되는 등 가시적인 성과를 거두고 있습니다.

KAIST의 시스템 혁신은 항상 국내외의 여러 기관으로부터 주목을 받았습니다. 국내 대학 최초로 도입된 테뉴어제도는 세부적인 보완을 통해 정착단계에 접어들었으며, 영어강의와 성적연계 등록금 제도 등은 구성원들의 적극적인 의견수렴과 전문가그룹의 심도있는 검토를 통해 보완‧발전되었습니다.

2013년 심도있는 경영진단을 바탕으로 행정조직의 대대적인 개편이 있었습니다. 기능통합과 의사결정 체계의 간소화를 목표로 단행된 행정조직개편은 KAIST 행정을 ‘변화에 유연히 대응하는 전략적 조직’, ‘핵심기능 중심의 효율적인 조직’, ‘적절하고 명확하게 역할이 부여된 합리적인 조직’, ‘고객지향적인 고객친화적 조직’으로 변화시켰습니다. 또한, 행정발전교육센터를 신설하여 적극투자함으로써 행정분야에서 근무하는 직원들이 지속적으로 자기계발을 할 수 있도록 장려하고, 행정업무에 실질적으로 도움을 줄 수 있는 강좌를 개설하여 행정역량을 제고함으로써 행정서비스의 질을 향상할 수 있도록 했습니다.

구성원들간 원활한 소통이 이루어질 수 있도록 다양한 채널을 설치하고 의견을 청취하는데 많은 노력을 기울였습니다. 우리나라 대학 최초로 총장자문기구로 옴부즈퍼슨 제도를 도입하여 학내에서 발생하는 다양한 고충을 청취하고 중재하였고, 고객만족센터를 설치하여 구성원에게 제공되는 학교서비스의 질을 제고하였으며, 인권윤리센터를 신설하여 인권‧윤리 침해 예방 및 신속한 피해구제를 통해 구성원의 인권을 보호하고 평등하고 다양성이 존중되는 캠퍼스 문화를 조성하였습니다. 총장과 학교 구성원간의 소통은 특정한 시간이나 특별한 기회를 만들어 하는 것이 아니라 상시 자연스럽게 이루어져야 합니다. 총장실 개방, 찾아가는 커피아워, 학부 및 대학원생 초청 간담회, 구성원과의 이메일 교환 등을 통해 여러분의 작은 목소리에도 귀를 기울이려고 적극적으로 노력했고, 교내를 오가며 우연히 만나 나눈 대화들 또한 학교를 운영하는데 큰 도움이 되었습니다.

우리학교는 대전시민들로부터 큰 사랑과 관심을 받고 있습니다. 대전광역시청, 유성구청, 충남대학교 등 지역의 여러 기관들과 긴밀히 소통하며 더불어 사는 길을 마련하고자 노력했습니다. 그 결과, 충남대학교와 우리학교 사이에 위치한 담을 허물고 열린길을 만들었고, 카이스트교를 개통하여 대전시민들에게 한발짝 더 다가가는 계기를 마련하였습니다. 한마음봉사단, 학생들의 김장봉사, 지역의 소외계층을 위한 교육봉사 등을 통해 KAIST가 먼저 지역사회에 다가가는 활동을 장려하고 지원하였으며 이러한 활동은 앞으로도 적극적으로 활성화되어야 할 것입니다.

지난 4년간 지속적인 인프라 개선사업을 추진하여 세계적인 대학의 명성에 걸맞는 교육과 연구를 지원하고 양질의 생활환경을 제공할 수 있는 인프라가 구축되었습니다. 현재 정문술 2관 신축공사가 마무리 되었고, 학술문화창의관 신축과 중앙도서관 리모델링 사업이 진행 중입니다. 우리 캠퍼스는 Startup KAIST Studio 2 신축, 의학연구동(약국) 신축, International Village C동 리모델링, 반도체동(새늘동) 리모델링, 대강당 리모델링, 기계공학동 리모델링, Startup Village 리모델링, 서울캠퍼스 해정사와 8‧9호관 리모델링, 노천극장 리모델링, 화암기숙사 리모델링(예정), 에코 캠퍼스 구축(소나무 이식 등), 안전한 캠퍼스 구축(도로 및 보행자도로 개선 등) 등 신축공사와 노후건물 및 시설의 보수공사 등으로 빠르게 변화하였습니다. 인프라 확충사업 외에도, 문지캠퍼스에 IBS 사업단, 녹색교통대학원 등을 이전하여 기존 스페이스를 효율적으로 사용할 수 있는 방안에 대해 다양한 논의가 진행되고 있습니다.

국제화를 추구하고 다양성을 존중하는 문화는 앞으로 우리학교가 지속적으로 발전하는 원동력이 될 것입니다. 그동안 외국인 교원 10%, 외국인 학생 10%, 여성 교원 10%를 목표로 삼고 우수한 인재를 유치하기 위해 최선을 다한 결과 이제는 10:10:10 이니셔티브(Initiative)를 20:20:20 이니셔티브(Initiative)로 그 목표를 수정할 단계에 이르렀습니다. 나눔관 공동 Kitchen 환경개선, 교내 PODCAST를 통한 외국인 구성원들과의 소통, 할랄푸드 카페테리아(Hallal Food Cafeteria) 오픈, Bilingual 캠퍼스 구축사업, 해외 유수대학들과의 공동학위 프로그램 개설, 해외 인턴십 프로그램 확충, 젠더평등을 위한 제도개선, 여성휴게실 및 육아시설 개선 등 지금까지 우리가 기울였던 노력은 앞으로도 반드시 지속되어야 할 것입니다.

KAIST에 대한 국내외적 관심은 앞으로 더욱 커질 것으로 생각됩니다. 최근 4년간의 학부 지원자 경쟁률 추이가 가파르게 상승하고 있으며, 매우 우수한 학생들이 매년 입학하고 있습니다. 새내기는 물론 재학생들의 학교생활 만족도 또한 지속적으로 향상되면서 학생들의 학교에 대한 관심과 사랑으로 이어지고 있습니다. 최근 재학생, 동문, 학부모 등 우리학교와 직접적으로 관계된 분들의 기부가 급격히 늘어나는 새로운 기부문화가 형성되었고, 지난 4년간 기부건수는 2만 6천여건에 이르며 기부금 총액은 708억여원에 달합니다.국내외의 유수 기관에서 KAIST를 벤치마킹하기 위해 많은 분들이 찾아오고 있고, 몇몇 국가에서는 KAIST 분교를 자국에 설치해 달라는 요청을 한바 있습니다. 이러한 변화는 Happy Campus를 만들기 위한 우리 구성원들의 부단한 노력의 결과라고 생각합니다.

사랑하는 KAIST 가족 여러분,

2017년 신년사는 제가 KAIST 총장으로서 여러분께 드리는 마지막 신년사 입니다. 이사회에서 신임 총장 선임절차가 진행중이며, 2017년 2월 23일 이취임식을 끝으로 저는 여러분과 함께 했던 4년간의 KAIST 생활을 마치고 정들었던 교정을 떠납니다.

KAIST 총장으로서 제게 허락하는 시간까지 단 한 명의 구성원이라도 소외되지 않고 Happy Campus에서 꿈을 펼칠 수 있도록 최선을 다해 노력하겠습니다. 여러분과 함께 했던 지난 4년은 제게 큰 행복이자 영광이었습니다. KAIST를 세계 최고의 대학으로 성장시키고 해피 캠퍼스를 구축하기 위해 각자의 분야에서 헌신해 준 KAIST 전체 가족 여러분께 진심으로 감사드립니다.

여러분은 KAIST의 미래이자 대한민국을 이끌어가는 원동력입니다. 그동안 일구어낸 성과를 바탕으로 각자의 위치에서 인류와 국가의 발전에 공헌 할 수 있는 더욱 큰 꿈을 꾸고 그 꿈을 이루기 위해 최선을 다해주시길 바랍니다.

2017년은 우리 KAIST 가족 여러분의 모든 꿈이 실현되는 희망찬 한 해가 되기를 기원합니다. ‘제4차 산업혁명의 허브(hub)’이자 ‘Students-Centered, Faculty-Driven World’s Best Research University’를 향한 여러분의 도전을 응원합니다.

감사합니다.

2017년 1월 1일

KAIST 총장 강성모

2017.01.02

조회수 20984

-

이상엽 특훈교수, 세계경제포럼 생명공학 미래 위원회 공동의장 선임

〈 이 상 엽 교수 〉

우리 대학 생명화학공학과 이상엽 특훈교수가 올해 세계경제포럼에서 출범 예정인 글로벌 미래 위원회(Global Future Council) 중 생명공학(biotech) 위원회의 초대 공동의장으로 선임됐다.

11월 아랍에미리트에서 첫 번째 미팅을 실시하는 글로벌 미래 위원회는 4차 산업 혁명을 대비하기 위해 정부, 학계, 산업계, 시민사회, 예술 등 다양한 분야에서 800여 명의 학자들이 참여한다.

특히 글로벌 미래 네트워크는 각 35개의 위원회가 연결돼 있고, 25개의 회원국으로 구성된다.

그 중 생명공학 글로벌 미래 위원회는 토마스 코넬리(Thomas Connelly) 미국 화학회장, 티나 파노(Tina Fano) 노보자임스 社 수석부사장, 모스타파 로나기(Mostafa Ronaghi) 일루미나 社 최고기술책임자 등 생명공학 분야 권위자들과 법학, 윤리, 정책 등 비 바이오 분야 전문가 24명으로 구성된다.

이 교수는 크리스퍼(CRISPR) 기술로 잘 알려진 MIT-하버드 브로드연구소의 펭 장(Feng Zhang) 교수와 함께 2년 간 공동 의장을 맡아 위원회를 운영하게 된다. 또한 이 교수는 세계경제포럼의 제4차 산업혁명 글로벌 미래 위원회의 위원으로도 초청받아 활동한다.

이 교수는 “제 4차 산업혁명시대를 이끌 한 축인 생명공학 분야에서 세계가 함께할 좋은 추진 안을 도출하도록 노력하겠다”고 말했다.

또한 이 교수는 대사공학 분야에서 세계적인 연구 성과를 낸 공을 인정받아 오는 15일 아시아인 최초로 제임스 베일리 상을 수상할 예정이다.

이상엽 특훈교수, 세계경제포럼 생명공학 미래 위원회 공동의장 선임

〈 이 상 엽 교수 〉

우리 대학 생명화학공학과 이상엽 특훈교수가 올해 세계경제포럼에서 출범 예정인 글로벌 미래 위원회(Global Future Council) 중 생명공학(biotech) 위원회의 초대 공동의장으로 선임됐다.

11월 아랍에미리트에서 첫 번째 미팅을 실시하는 글로벌 미래 위원회는 4차 산업 혁명을 대비하기 위해 정부, 학계, 산업계, 시민사회, 예술 등 다양한 분야에서 800여 명의 학자들이 참여한다.

특히 글로벌 미래 네트워크는 각 35개의 위원회가 연결돼 있고, 25개의 회원국으로 구성된다.

그 중 생명공학 글로벌 미래 위원회는 토마스 코넬리(Thomas Connelly) 미국 화학회장, 티나 파노(Tina Fano) 노보자임스 社 수석부사장, 모스타파 로나기(Mostafa Ronaghi) 일루미나 社 최고기술책임자 등 생명공학 분야 권위자들과 법학, 윤리, 정책 등 비 바이오 분야 전문가 24명으로 구성된다.

이 교수는 크리스퍼(CRISPR) 기술로 잘 알려진 MIT-하버드 브로드연구소의 펭 장(Feng Zhang) 교수와 함께 2년 간 공동 의장을 맡아 위원회를 운영하게 된다. 또한 이 교수는 세계경제포럼의 제4차 산업혁명 글로벌 미래 위원회의 위원으로도 초청받아 활동한다.

이 교수는 “제 4차 산업혁명시대를 이끌 한 축인 생명공학 분야에서 세계가 함께할 좋은 추진 안을 도출하도록 노력하겠다”고 말했다.

또한 이 교수는 대사공학 분야에서 세계적인 연구 성과를 낸 공을 인정받아 오는 15일 아시아인 최초로 제임스 베일리 상을 수상할 예정이다.

2016.11.08

조회수 9846

-

꿈의 신소재 ‘그래핀’ 활용한 차세대 메모리 소자 개발

[그림] 기존 실리콘 기반 전하포획방식 플래쉬 메모리 소자에 그래핀 전극이 도입된 모식도

- Nano Letters지 발표,“기존 생산라인을 그대로 이용하여 바로 양산할 수 있는 차세대 플래시 메모리 소자”-

금속 전극을 그래핀*으로 대체하면 기존의 플래시 메모리** 소자의 성능과 신뢰도가 획기적으로 개선된다는 사실이 국내 연구진에 의해 규명되었다.

조병진 교수(한국과학기술원)가 주도한 이번 연구는 교육과학기술부(장관 이주호)와 한국연구재단(이사장 오세정)이 추진하는 중견연구자지원사업(도약연구)과 미래기반기술개발사업의 지원으로 수행되었고, 연구결과는 나노과학 분야의 권위 있는 학술지인 ‘Nano Letters"지에 온라인 속보(11월 22일)로 게재되었다.

(논문명 : Graphene Gate Electrode for MOS Structure-based Electronic Devices)

특히, 이번 연구성과는 그래핀이 먼 미래의 반도체 소자가 아닌 현재 양산 중인 반도체 소자에도 바로 활용할 수 있는 소재인 점을 증명한 첫 사례라는 점에서 그 의미가 크다.

* 그래핀(Graphene) : 흑연의 표면층을 한 겹만 떼어낸 탄소나노물질로, 높은 전도성과 전하 이동도를 갖고 있어 향후 응용 가능성이 높아 꿈의 신소재로 불림

** 플래시 메모리(Flash Memory) : 전원이 공급되지 않아도 저장된 정보를 계속 유지하는 컴퓨터 기억장치의 일종으로, 스마트폰, 노트북, 디지털 카메라 등 전자장치에 폭넓게 사용됨

조병진 교수 연구팀은 기존의 실리콘 기반의 반도체 소자(전계효과 트랜지스터*)에서 금속 게이트 전극을 그래핀 전극으로 대체하면, 미래의 반도체 시장에서 요구하는 성능과 신뢰도를 확보할 수 있다는 사실을 밝혀냈다. 이 기술은 기존의 반도체 제조 공정에서 크게 바뀌는 부분이 없어서 머지않아 양산에 적용할 수 있다.

* 전계효과 트랜지스터(field effect transistor) : 전압(게이트 전압)으로 전류(드레인 전류)를 제어하는 형식의 가장 일반적이고 광범위하게 쓰이고 있는 반도체 소자

최근 그래핀의 우수한 전기적 특성을 활용하여 초고속 반도체, 신개념 로직 반도체* 등을 구현하기 위해 전 세계적으로 활발히 연구되고 있지만, 10~20년 후에나 상용화될 수 있는 기초․원천연구가 대부분이다.

※ 로직(Logic) 반도체 : 기억 기능을 하는 메모리 반도체와는 달리 데이터를 연산․처리하는 반도체

또한 지금까지 그래핀을 현재 세계 반도체 시장의 핵심 주류인 실리콘 기반 전자소자의 한 부분으로서 적용한 적은 없었다.

현재 국내외 기업에서는 20나노미터* 이하 급에서 사용될 것으로 예상되는 전하포획방식**의 플래시 메모리 소자를 연구 개발 중이다. 하지만 이 방식의 플래시 소자는 데이터 보존 특성이 시장의 요구조건(멀티비트 동작 시 섭씨 150도에서 10년 이상 데이터 보존 등)을 아직 충족시키지 못해 현재까지 대량으로 상용화되지 못하고 있다.

* 나노미터(nano meter) : 10억분의 1미터로, 1나노미터는 대략 성인 머리카락 굵기의 10만분의 1

** 전하포획 플래시(Charge Trap Flash) 메모리 : 전하를 기존의 도체가 아닌 부도체 물질에 저장하는 방식으로, 새로운 반도체 나노공정을 이용해 개발한 비휘발성 메모리

그러나 이번 성과는 현재 국내외 기업들이 집중적으로 연구개발하고 있는 전하포획방식의 플래시 메모리 소자에 그래핀 전극을 사용하면, 데이터 보존 특성이 바로 시판할 수 있는 성능과 신뢰도로 크게 개선(데이터 10% 손실시간 기준으로 기존 소자에 비해 10,000배 개선)될 뿐만 아니라, 데이터 씀과 지움 간의 전압차이가 70%나 개선되는 등 20나노미터이하의 플래시 메모리 소자의 상용화에 가장 큰 기술적 장벽을 극복할 수 있음을 실험으로 증명하였다.

이것은 그래핀이 세상에서 존재할 수 있는 가장 얇은 단원자층 물질이고 신축성과 유연성이 뛰어나, 기존의 금속 전극과는 달리 전극 아래에 위치한 게이트 유전막에 기계적 스트레스를 발생시키지 않기 때문인 것으로 확인되었다. 또한 이번 연구를 통해 그래핀이 갖는 큰 일함수*도 데이터 보존 특성을 향상시킬 수 있는 또 다른 장점으로 파악되었다.

※ 일함수(Work function) : 물질 내에 있는 전자 하나를 밖으로 끌어내는데 필요한 최소의 일(에너지)

조병진 교수는 “이번 연구결과는 새로운 나노기술을 기존의 반도체기술에 융합하여 기존 기술의 한계를 극복한 대표적인 예로서, 그래핀이 먼 미래만의 소재가 아닌 지금 또는 바로 다음 세대 반도체 핵심 소자에 즉시 적용될 수 있음을 보여주는 첫 사례이다. 또한 이번 연구결과를 응용해서 그래핀을 플래시 메모리 소자뿐만 아니라 자동차 전자제어장치, 군사용 및 의료 시스템 등 반도체 소자의 신뢰성이 특별히 중요한 분야에 폭넓게 활용될 수 있을 것으로 기대한다”고 밝혔다.

조병진 교수와 함께 이번 연구에 함께 참여한 연구팀, (뒷줄 왼쪽부터) 신우철 학생, 박종경 학생, 송승민 학생

꿈의 신소재 ‘그래핀’ 활용한 차세대 메모리 소자 개발

[그림] 기존 실리콘 기반 전하포획방식 플래쉬 메모리 소자에 그래핀 전극이 도입된 모식도

- Nano Letters지 발표,“기존 생산라인을 그대로 이용하여 바로 양산할 수 있는 차세대 플래시 메모리 소자”-

금속 전극을 그래핀*으로 대체하면 기존의 플래시 메모리** 소자의 성능과 신뢰도가 획기적으로 개선된다는 사실이 국내 연구진에 의해 규명되었다.

조병진 교수(한국과학기술원)가 주도한 이번 연구는 교육과학기술부(장관 이주호)와 한국연구재단(이사장 오세정)이 추진하는 중견연구자지원사업(도약연구)과 미래기반기술개발사업의 지원으로 수행되었고, 연구결과는 나노과학 분야의 권위 있는 학술지인 ‘Nano Letters"지에 온라인 속보(11월 22일)로 게재되었다.

(논문명 : Graphene Gate Electrode for MOS Structure-based Electronic Devices)

특히, 이번 연구성과는 그래핀이 먼 미래의 반도체 소자가 아닌 현재 양산 중인 반도체 소자에도 바로 활용할 수 있는 소재인 점을 증명한 첫 사례라는 점에서 그 의미가 크다.

* 그래핀(Graphene) : 흑연의 표면층을 한 겹만 떼어낸 탄소나노물질로, 높은 전도성과 전하 이동도를 갖고 있어 향후 응용 가능성이 높아 꿈의 신소재로 불림

** 플래시 메모리(Flash Memory) : 전원이 공급되지 않아도 저장된 정보를 계속 유지하는 컴퓨터 기억장치의 일종으로, 스마트폰, 노트북, 디지털 카메라 등 전자장치에 폭넓게 사용됨

조병진 교수 연구팀은 기존의 실리콘 기반의 반도체 소자(전계효과 트랜지스터*)에서 금속 게이트 전극을 그래핀 전극으로 대체하면, 미래의 반도체 시장에서 요구하는 성능과 신뢰도를 확보할 수 있다는 사실을 밝혀냈다. 이 기술은 기존의 반도체 제조 공정에서 크게 바뀌는 부분이 없어서 머지않아 양산에 적용할 수 있다.

* 전계효과 트랜지스터(field effect transistor) : 전압(게이트 전압)으로 전류(드레인 전류)를 제어하는 형식의 가장 일반적이고 광범위하게 쓰이고 있는 반도체 소자

최근 그래핀의 우수한 전기적 특성을 활용하여 초고속 반도체, 신개념 로직 반도체* 등을 구현하기 위해 전 세계적으로 활발히 연구되고 있지만, 10~20년 후에나 상용화될 수 있는 기초․원천연구가 대부분이다.

※ 로직(Logic) 반도체 : 기억 기능을 하는 메모리 반도체와는 달리 데이터를 연산․처리하는 반도체

또한 지금까지 그래핀을 현재 세계 반도체 시장의 핵심 주류인 실리콘 기반 전자소자의 한 부분으로서 적용한 적은 없었다.

현재 국내외 기업에서는 20나노미터* 이하 급에서 사용될 것으로 예상되는 전하포획방식**의 플래시 메모리 소자를 연구 개발 중이다. 하지만 이 방식의 플래시 소자는 데이터 보존 특성이 시장의 요구조건(멀티비트 동작 시 섭씨 150도에서 10년 이상 데이터 보존 등)을 아직 충족시키지 못해 현재까지 대량으로 상용화되지 못하고 있다.

* 나노미터(nano meter) : 10억분의 1미터로, 1나노미터는 대략 성인 머리카락 굵기의 10만분의 1

** 전하포획 플래시(Charge Trap Flash) 메모리 : 전하를 기존의 도체가 아닌 부도체 물질에 저장하는 방식으로, 새로운 반도체 나노공정을 이용해 개발한 비휘발성 메모리

그러나 이번 성과는 현재 국내외 기업들이 집중적으로 연구개발하고 있는 전하포획방식의 플래시 메모리 소자에 그래핀 전극을 사용하면, 데이터 보존 특성이 바로 시판할 수 있는 성능과 신뢰도로 크게 개선(데이터 10% 손실시간 기준으로 기존 소자에 비해 10,000배 개선)될 뿐만 아니라, 데이터 씀과 지움 간의 전압차이가 70%나 개선되는 등 20나노미터이하의 플래시 메모리 소자의 상용화에 가장 큰 기술적 장벽을 극복할 수 있음을 실험으로 증명하였다.

이것은 그래핀이 세상에서 존재할 수 있는 가장 얇은 단원자층 물질이고 신축성과 유연성이 뛰어나, 기존의 금속 전극과는 달리 전극 아래에 위치한 게이트 유전막에 기계적 스트레스를 발생시키지 않기 때문인 것으로 확인되었다. 또한 이번 연구를 통해 그래핀이 갖는 큰 일함수*도 데이터 보존 특성을 향상시킬 수 있는 또 다른 장점으로 파악되었다.

※ 일함수(Work function) : 물질 내에 있는 전자 하나를 밖으로 끌어내는데 필요한 최소의 일(에너지)

조병진 교수는 “이번 연구결과는 새로운 나노기술을 기존의 반도체기술에 융합하여 기존 기술의 한계를 극복한 대표적인 예로서, 그래핀이 먼 미래만의 소재가 아닌 지금 또는 바로 다음 세대 반도체 핵심 소자에 즉시 적용될 수 있음을 보여주는 첫 사례이다. 또한 이번 연구결과를 응용해서 그래핀을 플래시 메모리 소자뿐만 아니라 자동차 전자제어장치, 군사용 및 의료 시스템 등 반도체 소자의 신뢰성이 특별히 중요한 분야에 폭넓게 활용될 수 있을 것으로 기대한다”고 밝혔다.

조병진 교수와 함께 이번 연구에 함께 참여한 연구팀, (뒷줄 왼쪽부터) 신우철 학생, 박종경 학생, 송승민 학생

2011.11.21

조회수 16971

-

전기및전자공학과 박사과정 이재진 '2009 전파방송분야 논문제안 공모전' 회장상 수상

우리학교 정보통신공학과 박사과정 이재진 학생(지도교수 박철순)이 한국전파진흥원과 한국전자파학회에서 주관한 "제8회 2009 전파방송분야 논문제안 공모전"에서 회장상을 수상했다.

회장상을 수상한 이재진 학생은 "차세대 밀리미터파 대역 WPAN용 60GHz CMOS SoC" 논문으로 이 상을 수상하게 됐다.

관련 홈페이지 : http://www.kees.or.kr/korea/news/news01_2.php?board_idx=2&board_num=75

전기및전자공학과 박사과정 이재진 '2009 전파방송분야 논문제안 공모전' 회장상 수상

우리학교 정보통신공학과 박사과정 이재진 학생(지도교수 박철순)이 한국전파진흥원과 한국전자파학회에서 주관한 "제8회 2009 전파방송분야 논문제안 공모전"에서 회장상을 수상했다.

회장상을 수상한 이재진 학생은 "차세대 밀리미터파 대역 WPAN용 60GHz CMOS SoC" 논문으로 이 상을 수상하게 됐다.

관련 홈페이지 : http://www.kees.or.kr/korea/news/news01_2.php?board_idx=2&board_num=75

2009.11.10

조회수 8699

-

박사과정 이재진 '전파방송분야 논문공모전' 회장상 수상

우리학교 정보통신공학과 박사과정 이재진 학생(지도교수 박철순)이 한국전파진흥원과 한국전자파학회에서 주관한 "제8회 2009 전파방송분야 논문제안 공모전"에서 회장상을 수상했다.

회장상을 수상한 이재진 학생은 "차세대 밀리미터파 대역 WPAN용 60GHz CMOS SoC" 논문으로 이 상을 수상하게 됐다.

관련 홈페이지 : http://www.kees.or.kr/korea/news/news01_2.php?board_idx=2&board_num=75

박사과정 이재진 '전파방송분야 논문공모전' 회장상 수상

우리학교 정보통신공학과 박사과정 이재진 학생(지도교수 박철순)이 한국전파진흥원과 한국전자파학회에서 주관한 "제8회 2009 전파방송분야 논문제안 공모전"에서 회장상을 수상했다.

회장상을 수상한 이재진 학생은 "차세대 밀리미터파 대역 WPAN용 60GHz CMOS SoC" 논문으로 이 상을 수상하게 됐다.

관련 홈페이지 : http://www.kees.or.kr/korea/news/news01_2.php?board_idx=2&board_num=75

2009.11.09

조회수 12165

-

차세대 투명 저항 변화 메모리(TRRAM) 세계 최초 개발

- KAIST 전자전산학부 임굉수, 박재우 교수 연구팀

- 美 물리학회지, 응용물리학회지, 외국 인터넷 매체에 소개

미래 다가올 투명전자 기술의 밑거름이 되는 투명 메모리 소자가 국내 연구진에 의해 세계최초로 개발됐다.

KAIST 전자전산학부 임굉수(林宏樹, 62), 박재우(朴在佑, 44) 교수팀은 금속 산화물의 저항 변화를 이용한 차세대 투명 저항 변화 메모리(Transparent Resistive Random Access Memory: TRRAM) 소자 개발에 성공하여 미국 응용물리학회지(Applied Physics Letters) 12월호에 발표하였으며, 미국 물리학회(American Institute of Physics, 12월 9일자)로부터 주목 받는 기술로 선정되어 보도자료(Press Release: The Clear Future of Electronics)로 소개 되었다.

특히, 각종 외국 인터넷 뉴스매체에서도 이번에 개발된 투명 메모리 소자가 세계 1위 휴대폰 제조업체인 노키아에서 제안한 차세대 투명 휴대폰(일명: Morphy)에도 적용이 가능하다는 기사들을 게재했다.

이번에 개발된 투명 메모리 소자는 현재 일반인들이 주머니 속에 하나씩 가지고 다니는 USB형태의 플래시 메모리와 같이 전원이 제거되어도 저장된 데이터가 지워지지 않는 비휘발성 메모리 소자와 같은 종류이지만 투명 유리 또는 투명 플라스틱 기판 위에 투명 전극과 투명 산화물 박막 등으로만 구성되어 있어 전체적으로 투명하게 보이며, 기존 실리콘 기반 CMOS(상보적 금속/산화물/반도체) 플래시 메모리 소자보다 제조 공정이 훨씬 간단하고 사용 수명도 10년 이상으로 예상된다. 이 투명 메모리 소자는 기술적으로는 이미 상업개발이 진행되고 있는 저항 변화 메모리(RRAM)를 응용한 것이며, 향후 투명디스플레이등과 같은 투명전자기기와 집적화하여 통합형 투명 전자시스템 구현도 가능하게 되었다.

이번 연구는 KAIST 전자전산학부 박사과정 서중원 학생, 지도교수 임굉수 교수, 그리고 박재우 교수가 공동으로 수행하였으며, 미래 투명전자 기술에서 저장 매체로서 핵심적일 것으로 예상되지만 아직 연구 개발이 진행되지 않은 “완전히 투명한 메모리 소자”에 착안하여 연구 개발을 시작하게 되었다.

연구팀 관계자는 “이번 투명 메모리 소자 개발은 기존 실리콘 기반 CMOS 플래시 메모리 시장을 완전히 대체 하는 기술은 아니다” 며, “앞으로 다가올 투명 디스플레이 등과 같은 투명전자 시대에 맞춰 가장 기본적인 저장 매체인 메모리 소자 또한 투명하게 만들고자 하는 취지에서 개발되었고, 이와 더불어 앞으로도 IT 일등 강국으로서의 위상을 이어 나갈 수 있는 발판을 마련한 것에 의미가 있다고”고 밝혔다.

이번 연구는 KAIST BK21 사업 지원으로 수행되었다.

차세대 투명 저항 변화 메모리(TRRAM) 세계 최초 개발

- KAIST 전자전산학부 임굉수, 박재우 교수 연구팀

- 美 물리학회지, 응용물리학회지, 외국 인터넷 매체에 소개

미래 다가올 투명전자 기술의 밑거름이 되는 투명 메모리 소자가 국내 연구진에 의해 세계최초로 개발됐다.

KAIST 전자전산학부 임굉수(林宏樹, 62), 박재우(朴在佑, 44) 교수팀은 금속 산화물의 저항 변화를 이용한 차세대 투명 저항 변화 메모리(Transparent Resistive Random Access Memory: TRRAM) 소자 개발에 성공하여 미국 응용물리학회지(Applied Physics Letters) 12월호에 발표하였으며, 미국 물리학회(American Institute of Physics, 12월 9일자)로부터 주목 받는 기술로 선정되어 보도자료(Press Release: The Clear Future of Electronics)로 소개 되었다.

특히, 각종 외국 인터넷 뉴스매체에서도 이번에 개발된 투명 메모리 소자가 세계 1위 휴대폰 제조업체인 노키아에서 제안한 차세대 투명 휴대폰(일명: Morphy)에도 적용이 가능하다는 기사들을 게재했다.

이번에 개발된 투명 메모리 소자는 현재 일반인들이 주머니 속에 하나씩 가지고 다니는 USB형태의 플래시 메모리와 같이 전원이 제거되어도 저장된 데이터가 지워지지 않는 비휘발성 메모리 소자와 같은 종류이지만 투명 유리 또는 투명 플라스틱 기판 위에 투명 전극과 투명 산화물 박막 등으로만 구성되어 있어 전체적으로 투명하게 보이며, 기존 실리콘 기반 CMOS(상보적 금속/산화물/반도체) 플래시 메모리 소자보다 제조 공정이 훨씬 간단하고 사용 수명도 10년 이상으로 예상된다. 이 투명 메모리 소자는 기술적으로는 이미 상업개발이 진행되고 있는 저항 변화 메모리(RRAM)를 응용한 것이며, 향후 투명디스플레이등과 같은 투명전자기기와 집적화하여 통합형 투명 전자시스템 구현도 가능하게 되었다.

이번 연구는 KAIST 전자전산학부 박사과정 서중원 학생, 지도교수 임굉수 교수, 그리고 박재우 교수가 공동으로 수행하였으며, 미래 투명전자 기술에서 저장 매체로서 핵심적일 것으로 예상되지만 아직 연구 개발이 진행되지 않은 “완전히 투명한 메모리 소자”에 착안하여 연구 개발을 시작하게 되었다.

연구팀 관계자는 “이번 투명 메모리 소자 개발은 기존 실리콘 기반 CMOS 플래시 메모리 시장을 완전히 대체 하는 기술은 아니다” 며, “앞으로 다가올 투명 디스플레이 등과 같은 투명전자 시대에 맞춰 가장 기본적인 저장 매체인 메모리 소자 또한 투명하게 만들고자 하는 취지에서 개발되었고, 이와 더불어 앞으로도 IT 일등 강국으로서의 위상을 이어 나갈 수 있는 발판을 마련한 것에 의미가 있다고”고 밝혔다.

이번 연구는 KAIST BK21 사업 지원으로 수행되었다.

2008.12.16

조회수 16796

문화기술대학원, 제4회 디지털유산 국제심포지엄 개최

우리 대학이 23일(목)부터 이틀간 '제4회 디지털유산 국제심포지엄 개최(The 4th International Symposium on Digital Heritage; ISDH)'을 학술문화관 양승택 오디토리움에서 개최한다.'데이터로서의 문화유산: 유산 보존 관리 및 활용을 위한 디지털 방법론 개발을 선도하는 데이터 중심의 접근 전략'을 주제로 열리는 이번 심포지엄은 문화재청이 주최하고 우리 대학 문화기술대학원이 주관해 디지털헤리티지랩(안재홍, 심혜승)에서 총괄을 맡았다. 특히 이번 행사는 2025년 CIPA 심포지엄*을 우리 대학이 문화재청과 함께 한국에 유치한 것을 기념하기 위해 기획됐다. *CIPA(International Committee of Architectural Photogrammetry) 심포지엄: 1971년 시작되어 현재 2년마다 개최되는 학술대회로, 고고학, 건축학, 보존과학, 디지털 유산 등에서 최신 연구와 기술을 공유하기 위해 다양한 국가와 전문가들이 참여한다. 이를 위해, 디지털유산 분야에서 활발하게 활동하고 있는 국내외 석학 12명이 강연자로 참여한다. 행사 첫날에는 '비전과 미래: 데이터와 문화유산 보존 관리와 활용'을 주제로 한 플레너리 세션과 '데이터로서의 문화유산'을 주제로 한 전문가 토론, 특별 세션이 진행된다.

유럽 타임머신 프로젝트 독일 대사인 샌더 뮨스터(Sander Munster) 독일 프리드리히 실러 예나 대학교 디지털인문학과 교수, 이원재 문화기술대학원 교수, 첸양(Chen Yang) 중국 통지대학교 건축도시계획대학 부교수 겸 호주 퀸즐랜드대학교 건축학부 명예 선임연구원, 유정민 한국전통문화대학교 문화유산산업학과 교수 등 4명의 석학이 강연을 진행한다. 데이터가 중심이 되는 시대를 맞아 국내 디지털유산 분야의 나아갈 방향을 논의하는 두 번째 세션에서는 이코모스* CIPA 명예 위원장이자 이코모스 인터내셔널 사무총장을 역임한 마리오 산타나 퀸테로(Mario Santana Quintero) 캐나다 칼튼대학교 건설환경공학부 교수가 세션 1의 발제자들과 함께 토론을 진행한다. *이코모스(International Council on Monuments and Sites, ICOMOS): 국제기념물유적협의회

이어지는 특별 세션에서는 안재홍 문화기술대학원 교수가 '디지털유산 워킹그룹 설립: 조직 구성 및 운영 방향'을 제안한다. 유정민 한국전통문화대학교 문화유산산업학과 교수, 조영훈 공주대학교 문화재보존과학과 교수, 강동석 동국대학교 고고미술사학과 교수, 강현 국립문화재연구원 건축문화재연구실 연구관이 참여해 국내 디지털유산 분야의 발전을 촉진하기 위한 전문가 네트워킹에 대한 의견과 계획을 공유한다. 둘째 날인 24일은 2025년 CIPA 심포지엄을 위한 교육 프로그램을 중심으로 운영된다. '디지털유산과의 만남'을 주제로 열리는 세션 1에서는 마리오 산타나 퀸테로(Mario Santana Quintero) 교수, 토마스 리고트(Thomas Rigauts) 유네스코 세계유산센터 파리본부 사업운영전문관, 조 칼라스(Joe Kallas) 유네스코 컨설턴트, 미셀 두엉(Michelle Duong) ICOMOS CIPA 집행이사회 이사가 강연한다. 이어, '문화유산과 데이터 및 AI 기술'을 주제로 문화유산 데이터 기반의 AI 음성 도슨트 개발 실습 워크숍이 진행된다. 사전 등록으로 참여한 학부생들이 디지털유산 분야에 대한 이해도를 높일 수 있도록 기획되었으며, 인공지능 교육 전문업체인 스코프랩스(Scopelabs)에서 실습을 맡는다. 다학제적 분야인 디지털유산을 체험할 수 있도록 역사, 문화유산, 공학 등 다양한 전공의 학생들이 팀을 이뤄 수행한다.

이동만 교학부총장은 환영사를 통해 "문화유산 보존을 통해 정체성을 확립하고 후세에 전하기 위한 인류 공동의 미션을 디지털 시대에 부합하게 발전시킬 수 있도록 문화재청과의 협력을 지속해서 강화할 것"이라고 전했다.

이번 심포지엄의 영상은 추후 문화재청을 통해 공개될 예정이며, 심포지엄 웹사이트( https://isdh2023.org/ )에서 관련 자료를 내려받을 수 있다.

2023.11.23 조회수 1399

문화기술대학원, 제4회 디지털유산 국제심포지엄 개최

우리 대학이 23일(목)부터 이틀간 '제4회 디지털유산 국제심포지엄 개최(The 4th International Symposium on Digital Heritage; ISDH)'을 학술문화관 양승택 오디토리움에서 개최한다.'데이터로서의 문화유산: 유산 보존 관리 및 활용을 위한 디지털 방법론 개발을 선도하는 데이터 중심의 접근 전략'을 주제로 열리는 이번 심포지엄은 문화재청이 주최하고 우리 대학 문화기술대학원이 주관해 디지털헤리티지랩(안재홍, 심혜승)에서 총괄을 맡았다. 특히 이번 행사는 2025년 CIPA 심포지엄*을 우리 대학이 문화재청과 함께 한국에 유치한 것을 기념하기 위해 기획됐다. *CIPA(International Committee of Architectural Photogrammetry) 심포지엄: 1971년 시작되어 현재 2년마다 개최되는 학술대회로, 고고학, 건축학, 보존과학, 디지털 유산 등에서 최신 연구와 기술을 공유하기 위해 다양한 국가와 전문가들이 참여한다. 이를 위해, 디지털유산 분야에서 활발하게 활동하고 있는 국내외 석학 12명이 강연자로 참여한다. 행사 첫날에는 '비전과 미래: 데이터와 문화유산 보존 관리와 활용'을 주제로 한 플레너리 세션과 '데이터로서의 문화유산'을 주제로 한 전문가 토론, 특별 세션이 진행된다.

유럽 타임머신 프로젝트 독일 대사인 샌더 뮨스터(Sander Munster) 독일 프리드리히 실러 예나 대학교 디지털인문학과 교수, 이원재 문화기술대학원 교수, 첸양(Chen Yang) 중국 통지대학교 건축도시계획대학 부교수 겸 호주 퀸즐랜드대학교 건축학부 명예 선임연구원, 유정민 한국전통문화대학교 문화유산산업학과 교수 등 4명의 석학이 강연을 진행한다. 데이터가 중심이 되는 시대를 맞아 국내 디지털유산 분야의 나아갈 방향을 논의하는 두 번째 세션에서는 이코모스* CIPA 명예 위원장이자 이코모스 인터내셔널 사무총장을 역임한 마리오 산타나 퀸테로(Mario Santana Quintero) 캐나다 칼튼대학교 건설환경공학부 교수가 세션 1의 발제자들과 함께 토론을 진행한다. *이코모스(International Council on Monuments and Sites, ICOMOS): 국제기념물유적협의회

이어지는 특별 세션에서는 안재홍 문화기술대학원 교수가 '디지털유산 워킹그룹 설립: 조직 구성 및 운영 방향'을 제안한다. 유정민 한국전통문화대학교 문화유산산업학과 교수, 조영훈 공주대학교 문화재보존과학과 교수, 강동석 동국대학교 고고미술사학과 교수, 강현 국립문화재연구원 건축문화재연구실 연구관이 참여해 국내 디지털유산 분야의 발전을 촉진하기 위한 전문가 네트워킹에 대한 의견과 계획을 공유한다. 둘째 날인 24일은 2025년 CIPA 심포지엄을 위한 교육 프로그램을 중심으로 운영된다. '디지털유산과의 만남'을 주제로 열리는 세션 1에서는 마리오 산타나 퀸테로(Mario Santana Quintero) 교수, 토마스 리고트(Thomas Rigauts) 유네스코 세계유산센터 파리본부 사업운영전문관, 조 칼라스(Joe Kallas) 유네스코 컨설턴트, 미셀 두엉(Michelle Duong) ICOMOS CIPA 집행이사회 이사가 강연한다. 이어, '문화유산과 데이터 및 AI 기술'을 주제로 문화유산 데이터 기반의 AI 음성 도슨트 개발 실습 워크숍이 진행된다. 사전 등록으로 참여한 학부생들이 디지털유산 분야에 대한 이해도를 높일 수 있도록 기획되었으며, 인공지능 교육 전문업체인 스코프랩스(Scopelabs)에서 실습을 맡는다. 다학제적 분야인 디지털유산을 체험할 수 있도록 역사, 문화유산, 공학 등 다양한 전공의 학생들이 팀을 이뤄 수행한다.

이동만 교학부총장은 환영사를 통해 "문화유산 보존을 통해 정체성을 확립하고 후세에 전하기 위한 인류 공동의 미션을 디지털 시대에 부합하게 발전시킬 수 있도록 문화재청과의 협력을 지속해서 강화할 것"이라고 전했다.

이번 심포지엄의 영상은 추후 문화재청을 통해 공개될 예정이며, 심포지엄 웹사이트( https://isdh2023.org/ )에서 관련 자료를 내려받을 수 있다.

2023.11.23 조회수 1399 3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14 조회수 49219

3차원 적층형 화합물 반도체 소자 제작 성공

우리 대학 전기및전자공학부 김상현 교수 연구팀이 *모놀리식 3차원 집적의 장점을 극대화해 기존의 통신 소자의 단점을 극복하는 화합물 반도체 소자 집적 기술을 개발했다고 14일 밝혔다.

☞ 모놀리식 3차원 집적: 하부 소자 공정 후, 상부의 박막층을 형성하고 상부 소자 공정을 순차적으로 진행함으로써 상하부 소자 간의 정렬도를 극대화할 수 있는 기술로 궁극적 3차원 집적 기술로 불린다.

우리 대학 전기및전자공학부 정재용 박사과정이 제1 저자로 주도하고 한국나노기술원 김종민 박사, 광주과학기술원 장재형 교수 연구팀과의 협업으로 진행한 이번 연구는 반도체 올림픽이라 불리는 ‘VLSI 기술 심포지엄(Symposium on VLSI Technology)’에서 발표됐다. (논문명 : High-performance InGaAs-On-Insulator HEMTs on Si CMOS for Substrate Coupling Noise-free Monolithic 3D Mixed-Signal IC).

VLSI 기술 심포지엄은 국제전자소자학회(International Electron Device Meetings, IEDM)와 더불어 대학 논문의 채택비율이 25%가 되지 않는 저명한 반도체 소자 분야 최고 권위 학회다.

반도체 소자는 4차 산업 혁명의 특징인 초연결성 구현을 위한 핵심 통신 소재 및 부품으로서 주목받고 있다.

특히 통신 신호, 양자 신호는 아날로그 형태의 신호이고 신호전달 과정에서 신호의 크기가 약해지거나 잡음이 생겨 신호의 왜곡이 생기기도 한다. 따라서 이러한 신호를 주고받을 때 고속으로 신호의 증폭이 필요한데 이러한 증폭 소자에서는 초고속, 고출력, 저전력, 저잡음 등의 특성이 매우 중요하다. 또한 통신 기술이 발전함에 따라 이를 구성하는 시스템은 점점 더 복잡해져 고집적 소자 제작기술이 매우 중요하다.

통신 소자는 통상적으로 두 가지 방식으로 구현된다. 실리콘(Si)을 사용해 집적도 높은 Si CMOS를 이용해 증폭 소자를 구현하는 방법과 *III-V 화합물 반도체를 증폭 소자로 제작하고 기타 소자들을 Si CMOS로 제작해 패키징 하는 방식이 있다. 그러나 각각의 방식은 단점이 존재한다. 기존의 실리콘(Si) 기술은 물성적 한계로 인해 차단주파수 특성 등 통신 소자에 중요한 소자 성능 향상이 어려우며 기판 커플링 잡음 등 복잡한 신호 간섭에 의한 잡음 증가 문제가 존재한다. 반면, III-V 화합물 반도체 기술은 소자 자체의 잡음 특성은 우수하지만 다른 부품과의 집적/패키징 공정이 복잡하고 이러한 패키징 공정으로 인해 신호의 손실이 발생하는 문제가 존재한다.

☞ III-V 화합물 반도체: 주기율표 III족 원소와 V족 원소가 화합물을 이루고 있는 반도체로 전하 수송 특성 및 광 특성이 매우 우수한 소재

연구팀은 이러한 문제 해결을 위해 증폭 소자 이외의 소자 및 디지털 회로에서 좋은 성능을 낼 수 있는 Si CMOS 기판 위에 아날로그 신호 증폭 성능이 매우 우수한 III-V 화합물 반도체 *HEMT를 3차원 집적해 Si CMOS와 III-V HEMT의 장점을 극대화하는 공정 및 소자 구조를 제시했다. 3층으로 소자를 쌓아나감으로써 같은 기판 위에 집적할 수 있는 방식이다. 이와 동시에 기판 신호 간섭에 의한 잡음을 제거할 수 있음을 증명했다.

☞ HEMT: High-Electron Mobility Transistor

연구팀은 하부 Si CMOS의 성능 저하 방지를 위해 300oC 이하에서 상부 III-V 소자를 집적하는 웨이퍼 본딩 등의 초저온 공정을 활용해 상부 소자 집적 후에도 하부 Si CMOS의 성능을 그대로 유지할 수 있었다.

또한 고성능 상부 III-V 소자 제작을 위해서 InGaAs/InAs/InGaAs의 양자우물 구조를 도입해 높은 전자 수송 특성을 실현했으며 100 나노미터(nm) 노드 공정 수준으로도 세계 최고 수준의 차단 주파수 특성을 달성했다. 이는 10 나노미터(nm) 이하 급의 최첨단 공정을 사용하지 않고도 그 이상의 우수한 성능을 낼 수 있는 융합 기술로 향후 기존과 다른 형태의 파운드리 비즈니스 방식의 도입 가능성을 증명했다고 할 수 있다.

더불어 연구진은 이러한 3차원 집적 형태로 소자를 제작함으로써 기존에 SI CMOS에서 존재하는 기판 간섭에 의한 잡음을 해결할 수 있음을 실험을 통해 최초로 증명했다.

김상현 교수는 “디지털 회로 및 다양한 수동소자 제작에 최적화된 Si CMOS 기판 위에 증폭기 등의 능동소자 특성이 현존하는 어떤 물질보다 우수한 III-V 화합물 반도체 소자를 동시 집적할 가능성을 최초로 입증한 연구로, 향후 통신 소자 등에 응용이 가능할 것으로 생각한다”라며 “이번 기술은 향후 양자 큐빗의 해독 회로에도 응용할 수 있어 그 확장성이 매우 큰 기술이다. 다양한 분야에서 활용할 수 있도록 후속 연구에 힘쓰겠다”라고 말했다.

한편 이번 연구는 한국연구재단 지능형반도체기술개발사업, 경기도 시스템반도체 국산화 연구지원 사업 등의 지원을 받아 수행됐다.

2021.06.14 조회수 49219 정명수 교수, 테라바이트(TB) 메모리 시대 열어

*비휘발성 메모리(이하 NVDIMM)와 *초저지연 SSD(반도체 저장장치)가 하나의 메모리로 통합돼, 소수의 글로벌 기업만이 주도하고 있는 미래 *영구 메모리(Persistent Memory)보다 성능과 용량이 대폭 향상된 메모리 기술이 우리 연구진에 의해 개발됐다.

☞ 비휘발성 메모리(NVDIMM; Non-Volatile DIMM): 기존 D램(DRAM)에 플래시 메모리와 슈퍼 커패시터를 추가해 정전 때에도 데이터를 유지할 수 있는 메모리.

☞ 초저지연 SSD(Ultra Low Latency SSD): 기존 SSD를 개선해, 매우 낮은 지연시간을 갖는 SSD.

☞ 영구 메모리(Persistent Memory): 데이터의 보존성을 가지는 메모리.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 운영체제 연구실)이 비휘발성 메모리와 초저지연 SSD를 하나의 메모리 공간으로 통합하는 메모리-오버-스토리지(Memory-over-Storage, 이하 MoS) 기술 개발에 성공했다고 16일 밝혔다.

정 교수팀이 새롭게 개발한 이 기술은 기존 스토리지 기술을 재사용하는 데 인텔 옵테인 대비, 메모리 슬롯당 4배 이상인 테라바이트(TB=1,024GB) 수준의 저장 용량을 제공하면서도 휘발성 메모리(D램)과 유사한 사용자 수준의 데이터 처리 속도를 낼 수 있다.

기존 NVDIMM은 운영체제의 도움 없이 CPU가 직접 비휘발성 메모리에 접근할 수 있다는 장점이 있다. 반면 NVDIMM은 D램을 그대로 활용하고 배터리 크기를 무한히 키울 수 없기 때문에 대용량 데이터를 처리할 수 없다는 게 문제다. 이를 해결하기 위한 대안으로는 인텔의 옵테인 메모리 (Intel Optane DC PMM)와 메모리 드라이브 기술(Intel Memory Drive Technology) 등이 있다. 그러나 이러한 기술들은 비휘발성 메모리에 접근할 때마다 운영체제의 도움이 필요해 NVDIMM에 비해 50% 수준으로 읽기/쓰기 속도가 떨어진다.

정 교수팀이 제안한 MoS 기술은 초저지연 SSD를 주 메모리로 활용하고, NVDIMM을 *캐시메모리로 활용한다. 이 결과, SSD 대용량의 저장 공간을 사용자에게 메모리로 사용하게 해줌과 동시에 NVDIMM 단독 사용 시와 유사한 성능을 얻게 함으로써 미래 영구 메모리 기술들이 가지는 한계점을 전면 개선했다.

☞ 캐시: 자주 사용되는 데이터에 빨리 접근할 수 있도록 느린 메모리에 저장된 데이터를 빠른 메모리에 복사해 두는 기법.

MoS 기술은 메인보드나 CPU 내부에 있는 *메모리 컨트롤러 허브(이하 MCH)에 적용돼 사용자의 모든 메모리 요청을 처리한다. 사용자 요청은 일반적으로 NVDIMM 캐시 메모리에서 처리되지만 NVDIMM에 저장되지 않은 데이터의 경우 초저지연 SSD에서 데이터를 읽어와야 한다. 기존 기술들은 운영체제가 이러한 SSD 읽기를 처리하는 반면, 개발된 MoS 기술은 MCH 내부에서 하드웨어가 SSD 입출력을 직접 처리함으로써 초저지연 SSD에 접근 시 발생하는 운영체제(OS)의 입출력 오버헤드(추가로 요구되는 시간)를 완화하는 한편 SSD의 큰 용량을 일반 메모리처럼 사용할 수 있게 해준다.

☞ 메모리 컨트롤러 허브: 일반적으로 노스 브릿지(North Bridge)로 알려져 있으며, CPU가 메모리(DRAM)나 그래픽 처리장치(GPU)와 같은 고대역폭 장치에 접근할 수 있도록 도와주는 하드웨어.

정 교수가 이번에 개발한 MoS 기술은 소프트웨어 기반 메모리 드라이브나 옵테인 영구 메모리 기술 대비 45% 절감된 에너지 소모량으로 110%의 데이터 읽기/쓰기 속도 향상을 달성했다. 결과적으로 대용량의 메모리가 필요하고 정전으로 인한 시스템 장애에 민감한 데이터 센터, 슈퍼컴퓨터 등에 사용되는 기존 메모리/미래 영구 메모리를 대체할 수 있을 것으로 기대된다.

정명수 교수는 "미래 영구 메모리 기술은 일부 해외 유수 기업이 주도하고 있지만, 이번 연구성과를 기반으로 국내 기술과 기존 스토리 및 메모리 기술을 통해 관련 시장에서 우위를 선점할 수 있는 가능성을 열었다는 점에서 의미가 있다"고 강조했다.

이번 연구는 올해 6월에 열릴 컴퓨터 구조 분야 최우수 학술대회인 '이스카(ISCA, International Symposium on Computer Architecture), 2021'에 관련 논문(논문명: Revamping Storage Class Memory With Hardware Automated Memory-Over-Storage Solution)으로 발표될 예정이다. 또 해당 연구에 대한 자세한 내용은 연구실 웹사이트(http://camelab.org)에서 확인할 수 있다.

한편 이번 연구는 과학기술정보통신부와 한국연구재단이 추진하는 우수신진(중견연계) 사업, KAIST 정착연구사업 등의 지원을 받아 수행됐다.

2021.03.16 조회수 98570

정명수 교수, 테라바이트(TB) 메모리 시대 열어

*비휘발성 메모리(이하 NVDIMM)와 *초저지연 SSD(반도체 저장장치)가 하나의 메모리로 통합돼, 소수의 글로벌 기업만이 주도하고 있는 미래 *영구 메모리(Persistent Memory)보다 성능과 용량이 대폭 향상된 메모리 기술이 우리 연구진에 의해 개발됐다.

☞ 비휘발성 메모리(NVDIMM; Non-Volatile DIMM): 기존 D램(DRAM)에 플래시 메모리와 슈퍼 커패시터를 추가해 정전 때에도 데이터를 유지할 수 있는 메모리.

☞ 초저지연 SSD(Ultra Low Latency SSD): 기존 SSD를 개선해, 매우 낮은 지연시간을 갖는 SSD.

☞ 영구 메모리(Persistent Memory): 데이터의 보존성을 가지는 메모리.

우리 대학 전기및전자공학부 정명수 교수 연구팀(컴퓨터 아키텍처 및 운영체제 연구실)이 비휘발성 메모리와 초저지연 SSD를 하나의 메모리 공간으로 통합하는 메모리-오버-스토리지(Memory-over-Storage, 이하 MoS) 기술 개발에 성공했다고 16일 밝혔다.

정 교수팀이 새롭게 개발한 이 기술은 기존 스토리지 기술을 재사용하는 데 인텔 옵테인 대비, 메모리 슬롯당 4배 이상인 테라바이트(TB=1,024GB) 수준의 저장 용량을 제공하면서도 휘발성 메모리(D램)과 유사한 사용자 수준의 데이터 처리 속도를 낼 수 있다.

기존 NVDIMM은 운영체제의 도움 없이 CPU가 직접 비휘발성 메모리에 접근할 수 있다는 장점이 있다. 반면 NVDIMM은 D램을 그대로 활용하고 배터리 크기를 무한히 키울 수 없기 때문에 대용량 데이터를 처리할 수 없다는 게 문제다. 이를 해결하기 위한 대안으로는 인텔의 옵테인 메모리 (Intel Optane DC PMM)와 메모리 드라이브 기술(Intel Memory Drive Technology) 등이 있다. 그러나 이러한 기술들은 비휘발성 메모리에 접근할 때마다 운영체제의 도움이 필요해 NVDIMM에 비해 50% 수준으로 읽기/쓰기 속도가 떨어진다.

정 교수팀이 제안한 MoS 기술은 초저지연 SSD를 주 메모리로 활용하고, NVDIMM을 *캐시메모리로 활용한다. 이 결과, SSD 대용량의 저장 공간을 사용자에게 메모리로 사용하게 해줌과 동시에 NVDIMM 단독 사용 시와 유사한 성능을 얻게 함으로써 미래 영구 메모리 기술들이 가지는 한계점을 전면 개선했다.

☞ 캐시: 자주 사용되는 데이터에 빨리 접근할 수 있도록 느린 메모리에 저장된 데이터를 빠른 메모리에 복사해 두는 기법.

MoS 기술은 메인보드나 CPU 내부에 있는 *메모리 컨트롤러 허브(이하 MCH)에 적용돼 사용자의 모든 메모리 요청을 처리한다. 사용자 요청은 일반적으로 NVDIMM 캐시 메모리에서 처리되지만 NVDIMM에 저장되지 않은 데이터의 경우 초저지연 SSD에서 데이터를 읽어와야 한다. 기존 기술들은 운영체제가 이러한 SSD 읽기를 처리하는 반면, 개발된 MoS 기술은 MCH 내부에서 하드웨어가 SSD 입출력을 직접 처리함으로써 초저지연 SSD에 접근 시 발생하는 운영체제(OS)의 입출력 오버헤드(추가로 요구되는 시간)를 완화하는 한편 SSD의 큰 용량을 일반 메모리처럼 사용할 수 있게 해준다.

☞ 메모리 컨트롤러 허브: 일반적으로 노스 브릿지(North Bridge)로 알려져 있으며, CPU가 메모리(DRAM)나 그래픽 처리장치(GPU)와 같은 고대역폭 장치에 접근할 수 있도록 도와주는 하드웨어.

정 교수가 이번에 개발한 MoS 기술은 소프트웨어 기반 메모리 드라이브나 옵테인 영구 메모리 기술 대비 45% 절감된 에너지 소모량으로 110%의 데이터 읽기/쓰기 속도 향상을 달성했다. 결과적으로 대용량의 메모리가 필요하고 정전으로 인한 시스템 장애에 민감한 데이터 센터, 슈퍼컴퓨터 등에 사용되는 기존 메모리/미래 영구 메모리를 대체할 수 있을 것으로 기대된다.

정명수 교수는 "미래 영구 메모리 기술은 일부 해외 유수 기업이 주도하고 있지만, 이번 연구성과를 기반으로 국내 기술과 기존 스토리 및 메모리 기술을 통해 관련 시장에서 우위를 선점할 수 있는 가능성을 열었다는 점에서 의미가 있다"고 강조했다.

이번 연구는 올해 6월에 열릴 컴퓨터 구조 분야 최우수 학술대회인 '이스카(ISCA, International Symposium on Computer Architecture), 2021'에 관련 논문(논문명: Revamping Storage Class Memory With Hardware Automated Memory-Over-Storage Solution)으로 발표될 예정이다. 또 해당 연구에 대한 자세한 내용은 연구실 웹사이트(http://camelab.org)에서 확인할 수 있다.

한편 이번 연구는 과학기술정보통신부와 한국연구재단이 추진하는 우수신진(중견연계) 사업, KAIST 정착연구사업 등의 지원을 받아 수행됐다.

2021.03.16 조회수 98570 MOSFET보다 빠른 저전력 트랜지스터 개발

우리 대학 물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동 전력 소모량이 10배 이상 낮고 동작 속도가 2배 이상 빠른 저전력, 고속 터널 트랜지스터를 개발했다. 이제까지 구현된 저전력 트랜지스터 중 MOSFET보다 빠른 트랜지스터의 개발은 최초이다.

조 교수 연구팀은 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 붕화 질소 (hexagonal boron nitride)를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 상태 전류를 높이는데 성공했다. 이제까지의 저전력 트랜지스터는 전력 소모는 낮지만, 작동 상태 전류가 기존 MOSFET에 비해 현저히 작아서 작동 속도가 느린 문제점이 있었다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘나노 레터스 (Nano Letters)’ 4월 24일 자 온라인판에 게재됐다. (논문명 : Monolayer Hexagonal Boron Nitride Tunnel Barrier Contact for Low-Power Black Phosphorus Heterojunction Tunnel Field-Effect Transistors)

트랜지스터의 전력 소모를 감소시키기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 subthreshold swing (SS, 전류를 10배 증가시키는데 필요한 전압값, 단위: mV/decade = mV/dec)을 낮추는 것이 필요한데, 기존의 MOSFET은 thermal carrier injection mechanism 때문에 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다는 한계를 지닌다. band-to-band-tunneling을 carrier injection mechanism으로 가지는 터널 트랜지스터는 상온에서 SS 값이 60 mV/dec 미만으로 낮아질 수 있기 때문에 MOSFET을 대체할 수 있는 저전력 소자로 제안되어왔다. 지난 1월 조교수 연구팀은 흑린을 사용하여 60 mV/dec미만의 SS를 가지는 저전력 트랜지스터를 개발하는데 성공하여 Nature Nanotechnology에 결과를 보고하였다. 하지만, 그 결과 또한 여전히 작동 상태 전류, 특히 SS = 60 mV/dec인 지점에서의 전류가 0.6 μA/μm로 MOSFET의 threshold에서의 전류값 1-10μA/μm보다 낮은 한계가 있었다.

조 교수 연구팀은 본 연구에서 단층 붕화 질소를 활용하여 지난 연구의 한계를 극복하고 SS = 60mV/dec 지점에서의 작동 상태 전류를 Nature Nanotechnology에 보고한 저전력 흑린 트랜지스터에서의 결과보다 10배 이상 크고, MOSFET의 threshold에서의 전류값보다도 큰 20 μA/μm을 달성했다. 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 hexagonal boron nitride를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 속도를 높이는데 성공하여 저전력 고속 트랜지스터의 구성 요건을 완성했다는 점에서 큰 의의가 있다.

조성재 교수는 “흑린 이종접합 트랜지스터가 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동하는 것을 확인했다. 이는 기존 실리콘 기반의 MOSFET을 대체할 수 있는 새로운 트랜지스터의 가능성을 보여주는 결과이다.”라며 “이번 연구 결과를 바탕으로 기초 반도체 물리학 및 비메모리 반도체 산업에 다양한 응용이 가능할 것으로 기대한다.”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

2020.05.06 조회수 10679

MOSFET보다 빠른 저전력 트랜지스터 개발

우리 대학 물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동 전력 소모량이 10배 이상 낮고 동작 속도가 2배 이상 빠른 저전력, 고속 터널 트랜지스터를 개발했다. 이제까지 구현된 저전력 트랜지스터 중 MOSFET보다 빠른 트랜지스터의 개발은 최초이다.

조 교수 연구팀은 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 붕화 질소 (hexagonal boron nitride)를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 상태 전류를 높이는데 성공했다. 이제까지의 저전력 트랜지스터는 전력 소모는 낮지만, 작동 상태 전류가 기존 MOSFET에 비해 현저히 작아서 작동 속도가 느린 문제점이 있었다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘나노 레터스 (Nano Letters)’ 4월 24일 자 온라인판에 게재됐다. (논문명 : Monolayer Hexagonal Boron Nitride Tunnel Barrier Contact for Low-Power Black Phosphorus Heterojunction Tunnel Field-Effect Transistors)

트랜지스터의 전력 소모를 감소시키기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 subthreshold swing (SS, 전류를 10배 증가시키는데 필요한 전압값, 단위: mV/decade = mV/dec)을 낮추는 것이 필요한데, 기존의 MOSFET은 thermal carrier injection mechanism 때문에 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다는 한계를 지닌다. band-to-band-tunneling을 carrier injection mechanism으로 가지는 터널 트랜지스터는 상온에서 SS 값이 60 mV/dec 미만으로 낮아질 수 있기 때문에 MOSFET을 대체할 수 있는 저전력 소자로 제안되어왔다. 지난 1월 조교수 연구팀은 흑린을 사용하여 60 mV/dec미만의 SS를 가지는 저전력 트랜지스터를 개발하는데 성공하여 Nature Nanotechnology에 결과를 보고하였다. 하지만, 그 결과 또한 여전히 작동 상태 전류, 특히 SS = 60 mV/dec인 지점에서의 전류가 0.6 μA/μm로 MOSFET의 threshold에서의 전류값 1-10μA/μm보다 낮은 한계가 있었다.

조 교수 연구팀은 본 연구에서 단층 붕화 질소를 활용하여 지난 연구의 한계를 극복하고 SS = 60mV/dec 지점에서의 작동 상태 전류를 Nature Nanotechnology에 보고한 저전력 흑린 트랜지스터에서의 결과보다 10배 이상 크고, MOSFET의 threshold에서의 전류값보다도 큰 20 μA/μm을 달성했다. 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 트랜지스터 채널을 구성함으로써 전력소모를 줄이고, 단층 hexagonal boron nitride를 트랜지스터의 drain 접합에 이용해 터널 트랜지스터의 작동 속도를 높이는데 성공하여 저전력 고속 트랜지스터의 구성 요건을 완성했다는 점에서 큰 의의가 있다.

조성재 교수는 “흑린 이종접합 트랜지스터가 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동하는 것을 확인했다. 이는 기존 실리콘 기반의 MOSFET을 대체할 수 있는 새로운 트랜지스터의 가능성을 보여주는 결과이다.”라며 “이번 연구 결과를 바탕으로 기초 반도체 물리학 및 비메모리 반도체 산업에 다양한 응용이 가능할 것으로 기대한다.”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

2020.05.06 조회수 10679 저전력·고속 터널 전계효과 트랜지스터 개발

물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동전력 소모량이 10배 이상, 대기전력 소모량이 1만 배 가까이 적은 저전력, 고속 트랜지스터를 개발했다.

조 교수 연구팀은 2차원 물질인 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 두 물질의 접합이 아닌 단일 물질의 두께 차이에 의한 이종접합 터널을 제작하는 데 성공했다. 이러한 단일 물질의 이종접합을 터널 트랜지스터에 활용하면 서로 다른 물질로 제작한 이종접합 트랜지스터에서 발생했던 격자 불균형, 결함, 계면 산화 등의 문제를 해결할 수 있어 고성능 터널 트랜지스터의 개발이 가능하다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘네이처 나노테크놀로지 (Nature Nanotechnology)’ 1월 27일 자 온라인판에 게재됐다. (논문명 : Thickness-controlled black phosphorus tunnel field-effect transistor fro low-power switches).

무어 법칙에 따른 트랜지스터 소형화 및 집적도 증가는 현대의 정보화 기술을 가능하게 했지만 최근 트랜지스터의 소형화가 양자역학적 한계에 다다르면서 전력 소모가 급격히 증가해 이제는 무어 법칙에 따라 트랜지스터 소형화가 진행되지 못하는 상황이다. 최근에는 자율주행차, 사물인터넷 등의 등장으로 많은 양의 데이터를 저전력, 고속으로 처리할 수 있는 비메모리 반도체의 기술 발달이 시급히 요구되고 있다.

트랜지스터의 전력 소모는 크게 작동 전력 소모와 대기 전력 소모로 나뉜다. 작동 전력과 대기 전력을 같이 낮추기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 전류를 10배 증가시키는데 필요한 전압으로 정의되는 SS 값(subthreshold swing, 단위: mV/decade = mV/dec)의 감소가 필요한데, 금속 산화물 반도체 전계효과 트랜지스터에서는 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다. 이를 해결하기 위해서는 상온에서 SS 값을 60 mV/dec 이하로 낮출 수 있는 새로운 트랜지스터의 개발이 필요하다. 이전에 개발되었던 낮은 SS를 가지는 저전력 터널 트랜지스터의 경우 트랜지스터 채널을 구성하는 두 물질의 이종접합 계면에서 산화막 등의 문제가 발생하여 작동 상태에서 낮은 전류를 가지는 문제가 있었다. 작동 상태 전류는 트랜지스터 작동속도에 비례하기 때문에, 낮은 작동 상태 전류는 저전력 트랜지스터의 경쟁력을 떨어뜨린다.

조 교수 연구팀이 적은 전력소모를 위한 낮은 SS 값과 고속 작동을 위한 높은 작동 상태 전류를 단일 트랜지스터에서 동시에 달성한 것은 유례없는 일로 2차원 물질 기반의 저전력 트랜지스터가 기존의 금속 산화물 반도체 전계효과 트랜지스터의 전력 소모 문제를 해결하고, 궁극적으로 기존 트랜지스터를 대체하고 미래의 저전력 대체 트랜지스터가 될 수 있음을 의미한다. 조성재 교수는 “이번 연구는 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동해 실리콘 기반의 CMOS 트랜지스터를 대체할 수 있는 저전력 소자의 필요충분조건을 최초로 만족시킨 개발이다”라며 “대한민국 비메모리 산업뿐 아니라 세계적으로 기초 반도체 물리학 및 산업 응용에 큰 의의를 지닌다”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

2020.02.20 조회수 12893

저전력·고속 터널 전계효과 트랜지스터 개발

물리학과 조성재 교수 연구팀이 기존의 금속 산화물 반도체 전계효과 트랜지스터(metal-oxide-semiconductor field-effect transistor, MOSFET) 대비 작동전력 소모량이 10배 이상, 대기전력 소모량이 1만 배 가까이 적은 저전력, 고속 트랜지스터를 개발했다.

조 교수 연구팀은 2차원 물질인 흑린(black phosphorus)의 두께에 따라 밴드갭이 변하는 독특한 성질을 이용해 두 물질의 접합이 아닌 단일 물질의 두께 차이에 의한 이종접합 터널을 제작하는 데 성공했다. 이러한 단일 물질의 이종접합을 터널 트랜지스터에 활용하면 서로 다른 물질로 제작한 이종접합 트랜지스터에서 발생했던 격자 불균형, 결함, 계면 산화 등의 문제를 해결할 수 있어 고성능 터널 트랜지스터의 개발이 가능하다.

김성호 연구원이 1 저자로 참여한 이번 연구는 국제 학술지 ‘네이처 나노테크놀로지 (Nature Nanotechnology)’ 1월 27일 자 온라인판에 게재됐다. (논문명 : Thickness-controlled black phosphorus tunnel field-effect transistor fro low-power switches).

무어 법칙에 따른 트랜지스터 소형화 및 집적도 증가는 현대의 정보화 기술을 가능하게 했지만 최근 트랜지스터의 소형화가 양자역학적 한계에 다다르면서 전력 소모가 급격히 증가해 이제는 무어 법칙에 따라 트랜지스터 소형화가 진행되지 못하는 상황이다. 최근에는 자율주행차, 사물인터넷 등의 등장으로 많은 양의 데이터를 저전력, 고속으로 처리할 수 있는 비메모리 반도체의 기술 발달이 시급히 요구되고 있다.

트랜지스터의 전력 소모는 크게 작동 전력 소모와 대기 전력 소모로 나뉜다. 작동 전력과 대기 전력을 같이 낮추기 위해서는 트랜지스터의 작동 전압과 대기 상태 전류를 동시에 낮추는 것이 필수적이다. 이를 위해서는 전류를 10배 증가시키는데 필요한 전압으로 정의되는 SS 값(subthreshold swing, 단위: mV/decade = mV/dec)의 감소가 필요한데, 금속 산화물 반도체 전계효과 트랜지스터에서는 SS 값이 상온에서 60 mV/dec 이하로 낮아질 수 없다. 이를 해결하기 위해서는 상온에서 SS 값을 60 mV/dec 이하로 낮출 수 있는 새로운 트랜지스터의 개발이 필요하다. 이전에 개발되었던 낮은 SS를 가지는 저전력 터널 트랜지스터의 경우 트랜지스터 채널을 구성하는 두 물질의 이종접합 계면에서 산화막 등의 문제가 발생하여 작동 상태에서 낮은 전류를 가지는 문제가 있었다. 작동 상태 전류는 트랜지스터 작동속도에 비례하기 때문에, 낮은 작동 상태 전류는 저전력 트랜지스터의 경쟁력을 떨어뜨린다.

조 교수 연구팀이 적은 전력소모를 위한 낮은 SS 값과 고속 작동을 위한 높은 작동 상태 전류를 단일 트랜지스터에서 동시에 달성한 것은 유례없는 일로 2차원 물질 기반의 저전력 트랜지스터가 기존의 금속 산화물 반도체 전계효과 트랜지스터의 전력 소모 문제를 해결하고, 궁극적으로 기존 트랜지스터를 대체하고 미래의 저전력 대체 트랜지스터가 될 수 있음을 의미한다. 조성재 교수는 “이번 연구는 기존의 어떤 트랜지스터보다 저전력, 고속으로 작동해 실리콘 기반의 CMOS 트랜지스터를 대체할 수 있는 저전력 소자의 필요충분조건을 최초로 만족시킨 개발이다”라며 “대한민국 비메모리 산업뿐 아니라 세계적으로 기초 반도체 물리학 및 산업 응용에 큰 의의를 지닌다”라고 말했다.

이번 연구는 한국연구재단 미래반도체신소자원천기술개발사업의 지원을 받아 수행됐다.

2020.02.20 조회수 12893 KAIST, 2년 연속 아시아 최고 혁신대학 1위 선정

우리대학이 2017년 ‘로이터 랭킹-아시아 최고 혁신대학 75(Reuters Top 75: Asia’s Most Innovative Universities)' 순위에서 작년에 이어 올해에도 2년 연속 1위를 차지했다.

로이터는 클래리베이트 애널리틱스(Clarivate Analytics)와 공동으로 2010년부터 2015년까지 아시아 각 대학의 학술논문 및 특허출원 실적 등을 종합 분석해 2017년 아시아에서 가장 혁신적인 교육기관 상위 75개 대학의 순위를 매긴 후 그 결과를 8일 공개했다. 평가지표는 특허출원 수, 특허성공률, 국제특허, 특허인용 수, 특허인용 비율, 특허인용 논문 영향력, 산업계논문인용 영향력 등 10개다. 로이터는 이들 10개 지표를 모두 고려해 평가에 종합 반영함으로써 75개 대학의 순위를 결정한다.

올해로 2회째를 맞이한 이번 조사에서 우리대학은 아시아 최고 혁신대학으로 작년에 이어 2년 연속 1위를 차지했다. 우리대학은 로이터통신이 2009~2014년 자료를 기초로 산정한 2016년 혁신대학 순위에서 아시아 대학 중 1위를, 세계대학 중 6위를 각각 기록했다. 우리대학은 올해 평가에서 “2010년부터 2015년까지 923개의 특허를 신청해 75개 상위 교육기관 중 가장 많은 수의 특허를 출원했고 특허 성공률뿐만 아니라 외부 연구자들이 KAIST의 특허를 연구논문과 특허에 자주 인용했기 때문에 높은 점수를 받았다”고 로이터측은 밝혔다.

로이터가 8일 발표한 자료에 따르면 우리나라는 상위 5위 안에 우리대학을 포함한 4개의 대학이, 상위 20위 안에는 8개 대학을 배출하는 등 총 22개 대학이 상위 75개 대학 명단에 포함됐다. 홍콩을 포함한 중국이 25개로 1위를 차지했고 일본이 19개로 우리나라의 뒤를 이었다.

이밖에 호주(5개), 싱가포르(2개), 뉴질랜드(1개)와 인도(1개) 대학 순으로 조사됐다. 2017년 상위 20위권 안에 포함된 국내 대학은 △KAIST(1위) △서울대(2위) △포스텍(4위) △성균관대(5위) △한양대(10위) △연세대(14위) △고려대(15위) △GIST(광주과학기술원, 18위) 순이다.

한편 김진우 클래리베이트 애널리틱스 한국지사장은 오는 15일 오후 KAIST를 방문해 신성철 총장에게 우리대학이 ‘로이터 Top 75: 아시아 최고 혁신대학 2017’ 조사에서 1위로 선정된 내용을 담은 기념패를 전달할 예정이다.

2017.06.09 조회수 11012

KAIST, 2년 연속 아시아 최고 혁신대학 1위 선정

우리대학이 2017년 ‘로이터 랭킹-아시아 최고 혁신대학 75(Reuters Top 75: Asia’s Most Innovative Universities)' 순위에서 작년에 이어 올해에도 2년 연속 1위를 차지했다.

로이터는 클래리베이트 애널리틱스(Clarivate Analytics)와 공동으로 2010년부터 2015년까지 아시아 각 대학의 학술논문 및 특허출원 실적 등을 종합 분석해 2017년 아시아에서 가장 혁신적인 교육기관 상위 75개 대학의 순위를 매긴 후 그 결과를 8일 공개했다. 평가지표는 특허출원 수, 특허성공률, 국제특허, 특허인용 수, 특허인용 비율, 특허인용 논문 영향력, 산업계논문인용 영향력 등 10개다. 로이터는 이들 10개 지표를 모두 고려해 평가에 종합 반영함으로써 75개 대학의 순위를 결정한다.

올해로 2회째를 맞이한 이번 조사에서 우리대학은 아시아 최고 혁신대학으로 작년에 이어 2년 연속 1위를 차지했다. 우리대학은 로이터통신이 2009~2014년 자료를 기초로 산정한 2016년 혁신대학 순위에서 아시아 대학 중 1위를, 세계대학 중 6위를 각각 기록했다. 우리대학은 올해 평가에서 “2010년부터 2015년까지 923개의 특허를 신청해 75개 상위 교육기관 중 가장 많은 수의 특허를 출원했고 특허 성공률뿐만 아니라 외부 연구자들이 KAIST의 특허를 연구논문과 특허에 자주 인용했기 때문에 높은 점수를 받았다”고 로이터측은 밝혔다.

로이터가 8일 발표한 자료에 따르면 우리나라는 상위 5위 안에 우리대학을 포함한 4개의 대학이, 상위 20위 안에는 8개 대학을 배출하는 등 총 22개 대학이 상위 75개 대학 명단에 포함됐다. 홍콩을 포함한 중국이 25개로 1위를 차지했고 일본이 19개로 우리나라의 뒤를 이었다.

이밖에 호주(5개), 싱가포르(2개), 뉴질랜드(1개)와 인도(1개) 대학 순으로 조사됐다. 2017년 상위 20위권 안에 포함된 국내 대학은 △KAIST(1위) △서울대(2위) △포스텍(4위) △성균관대(5위) △한양대(10위) △연세대(14위) △고려대(15위) △GIST(광주과학기술원, 18위) 순이다.

한편 김진우 클래리베이트 애널리틱스 한국지사장은 오는 15일 오후 KAIST를 방문해 신성철 총장에게 우리대학이 ‘로이터 Top 75: 아시아 최고 혁신대학 2017’ 조사에서 1위로 선정된 내용을 담은 기념패를 전달할 예정이다.

2017.06.09 조회수 11012 2017년 총장 신년사

친애하는 KAIST 가족 여러분,

2017년 정유년(丁酉年) 새해가 밝았습니다. 새해 복 많이 받으시고, 댁내 건강과 행복이 가득하기를 기원합니다. 새해에도 여러분의 꿈이 이루어지고, 국민들로부터 큰 사랑과 믿음을 받고 있는 우리 KAIST가 그 성원에 보답할 수 있는 한해가 되기를 바랍니다.

2013년 총장으로 부임하며 Quantum Jump 전략을 수립하고, 전반기(2013~14)에는 ‘하나된 KAIST’를 만들어 구성원의 역량을 결집하고 후반기(2015~16)에는 ‘질적성장을 통해 혁신하는 KAIST’를 만들어 크게 도약하고자 노력했습니다. 지난 4년간 우리는 성장통을 지혜롭게 극복하며 눈부신 발전을 거듭했고, 명실상부한 ‘Students-Centered, Faculty-Driven, World’s Most Innovative Research University’로 발돋움 했습니다.

우리학교의 수월성을 달성하기 위한 ‘창의’와 ‘도전’은 국가발전의 원동력이 되어 왔습니다. 교육·연구·시스템의 지속적인 혁신, 창업문화의 확산, 대학의 사회적 책무를 다하고자 하는 노력들은 학교의 질적성장을 이끌어 왔습니다.

KAIST의 교육은 끊임없이 발전하고 있습니다. 세계적인 대학의 위상에 걸맞는 교육시스템을 마련하고자 세차례에 걸친 고강도 학사조직개편 끝에 미래지향적인 교육 플랫폼이 완성되었습니다. KAIST의 교육은 넓은 학문단위의 학사교육과 융합전공의 대학원교육이 효율적으로 운영될 수 있는 체제에 더하여 학문적 수월성과 창의성이 조화를 이루는 융합형 교육시스템입니다. 우리 학생들은 이러한 π(파이)형 교육시스템 속에서 학사과정간 학문적 기반의 공통점을 바탕으로 기초를 튼튼히 하고, 석‧박사 교육과정간 융합 전공교육과 연구를 통해 지혜와 지식을 체득하고 졸업 후 사회에 진출했을 때 대체불가능한 우수한 인재로 성장하고 있습니다.

새로 도입된 융합 Capstone Design 교과과정은 국내 공학교육의 패러다임을 현장중심형 교육으로 새롭게 바꾸는 계기를 마련했습니다. 본 과정을 통해 우리 학생들은 사회가 필요로 하는 과제를 직접 기획하고 도출된 문제를 해결해 봄으로써 창의성, 실무능력, 팀워크 및 리더십을 갖추게 될 것입니다.

우리학교는 Education 3.0을 통해 수요자 중심의 교육시스템을 선도하고 있습니다. 학생들은 강의 전에 제공받은 온라인 콘텐츠로 자기주도 사전학습을 수행하고, 수업시간에는 지식전달식 강의 대신 배움의 주체가 되어 팀원들과 협력학습을 하며 전공지식과 문제해결 및 소통능력 등을 체득하게 됩니다. 우리학교는 자체적으로 개발한 온라인 공개강좌 서비스인 KOOC(KAIST MOOC)을 개방함으로써 KAIST의 우수한 교육을 국내‧외에 무상으로 제공하며 대학의 사회적 책무를 다하고 있습니다.

KAIST의 연구역량은 세계적인 대학들과 어깨를 나란히 하고 있습니다. 우리학교의 혁신적인 교육 및 연구역량은 이미 QS, THE 등 세계 유수의 기관들로부터 널리 인정받고 있으며, 로이터통신은 매년 세계가 놀랄만한 연구성과를 발표하고 있는 우리학교를 ‘세계 혁신대학 6위’로 선정한바 있습니다. KAIST가 지금과 같이 지속적으로 발전하기 위해서는 단기적인 소나기 정책에 의한 연구보다는 늘 한 곳에서 샘솟는 샘물같이 지속가능한 연구를 수행할 수 있어야 합니다. 특히, 인류발전에 공헌할 수 있는 아이디어가 지속적으로 창출되고, 그 연구를 안정적으로 뒷받침 할 수 있는 재원이 마련되어야 하며, 누구나 꿈을 가지고 도전하며 도전의 성공여부 보다는 그 도전의 성실성이 평가되는 연구문화가 구축되어야 할 것입니다. KAIST 그랜드챌린지30 프로젝트와 같이 선도적인 연구지원제도를 신설한 것도 우리 KAIST가 앞장서서 인류가 당면한 거대한 문제들을 해결하고, 혁신적인 연구문화를 확산시키기 위함입니다.

생명과학분야의 글로벌 경쟁력을 확보하기 위해 그동안 KAIST 융합의과학대학원(세종)을 설립하기 위해 노력해왔습니다. 수년간 추진하였던 「KAIST 융합의과학대학원(세종) 설립사업」 예비타당성조사가 많은 분들의 노력으로 조만간 긍정적인 결과를 얻어 2018년부터 정부예산이 반영될 것으로 기대합니다. 우리학교는 융합의과학대학원을 시작으로 세종시에 KAIST의 혁신적인 교육·연구시스템을 구축하게 될 것이고, 융합생명과학분야의 경쟁력있는 교육‧연구역량을 갖추게 될 것입니다.

우리학교는 그동안 우리나라 대학사회의 창업문화를 선도하고 확산하는데 최선을 다해왔습니다. 학생들이 기업가정신을 함양할 수 있는 기회를 널리 제공하고 교원들의 창업활동을 장려함으로써 KAIST의 우수한 교육과 혁신적인 연구성과가 경제적‧사회적 가치로 연결될 수 있도록 노력했습니다. 과학기술 분야의 우수한 인재들이 창업인재로 성장할 수 있도록 지원하는 전담조직인 KAIST 창업원(Institute for Startup KAIST)을 설치하여 창의적인 아이디어가 사업화에 이르는 전 과정을 지원하고 있습니다. 또한 K-School을 설립하여 다양한 학과가 공동으로 운영하는 창업맞춤형 교육프로그램인 창업융합전문석사 과정을 운영하고 있습니다. 그 외에도 창업원 판교센터, KAIST 사회적기업가 MBA(SEMBA) 등 우리학교는 창업과 관련한 다양한 프로그램을 설치‧운영하며 캠퍼스 내 창업분위기를 조성하는 것은 물론 KAIST가 주축이 되어 전국적으로 창업문화가 확산될 수 있도록 노력한 결과 국내대학 창업지수 1위로 선정되는 등 가시적인 성과를 거두고 있습니다.

KAIST의 시스템 혁신은 항상 국내외의 여러 기관으로부터 주목을 받았습니다. 국내 대학 최초로 도입된 테뉴어제도는 세부적인 보완을 통해 정착단계에 접어들었으며, 영어강의와 성적연계 등록금 제도 등은 구성원들의 적극적인 의견수렴과 전문가그룹의 심도있는 검토를 통해 보완‧발전되었습니다.

2013년 심도있는 경영진단을 바탕으로 행정조직의 대대적인 개편이 있었습니다. 기능통합과 의사결정 체계의 간소화를 목표로 단행된 행정조직개편은 KAIST 행정을 ‘변화에 유연히 대응하는 전략적 조직’, ‘핵심기능 중심의 효율적인 조직’, ‘적절하고 명확하게 역할이 부여된 합리적인 조직’, ‘고객지향적인 고객친화적 조직’으로 변화시켰습니다. 또한, 행정발전교육센터를 신설하여 적극투자함으로써 행정분야에서 근무하는 직원들이 지속적으로 자기계발을 할 수 있도록 장려하고, 행정업무에 실질적으로 도움을 줄 수 있는 강좌를 개설하여 행정역량을 제고함으로써 행정서비스의 질을 향상할 수 있도록 했습니다.

구성원들간 원활한 소통이 이루어질 수 있도록 다양한 채널을 설치하고 의견을 청취하는데 많은 노력을 기울였습니다. 우리나라 대학 최초로 총장자문기구로 옴부즈퍼슨 제도를 도입하여 학내에서 발생하는 다양한 고충을 청취하고 중재하였고, 고객만족센터를 설치하여 구성원에게 제공되는 학교서비스의 질을 제고하였으며, 인권윤리센터를 신설하여 인권‧윤리 침해 예방 및 신속한 피해구제를 통해 구성원의 인권을 보호하고 평등하고 다양성이 존중되는 캠퍼스 문화를 조성하였습니다. 총장과 학교 구성원간의 소통은 특정한 시간이나 특별한 기회를 만들어 하는 것이 아니라 상시 자연스럽게 이루어져야 합니다. 총장실 개방, 찾아가는 커피아워, 학부 및 대학원생 초청 간담회, 구성원과의 이메일 교환 등을 통해 여러분의 작은 목소리에도 귀를 기울이려고 적극적으로 노력했고, 교내를 오가며 우연히 만나 나눈 대화들 또한 학교를 운영하는데 큰 도움이 되었습니다.

우리학교는 대전시민들로부터 큰 사랑과 관심을 받고 있습니다. 대전광역시청, 유성구청, 충남대학교 등 지역의 여러 기관들과 긴밀히 소통하며 더불어 사는 길을 마련하고자 노력했습니다. 그 결과, 충남대학교와 우리학교 사이에 위치한 담을 허물고 열린길을 만들었고, 카이스트교를 개통하여 대전시민들에게 한발짝 더 다가가는 계기를 마련하였습니다. 한마음봉사단, 학생들의 김장봉사, 지역의 소외계층을 위한 교육봉사 등을 통해 KAIST가 먼저 지역사회에 다가가는 활동을 장려하고 지원하였으며 이러한 활동은 앞으로도 적극적으로 활성화되어야 할 것입니다.

지난 4년간 지속적인 인프라 개선사업을 추진하여 세계적인 대학의 명성에 걸맞는 교육과 연구를 지원하고 양질의 생활환경을 제공할 수 있는 인프라가 구축되었습니다. 현재 정문술 2관 신축공사가 마무리 되었고, 학술문화창의관 신축과 중앙도서관 리모델링 사업이 진행 중입니다. 우리 캠퍼스는 Startup KAIST Studio 2 신축, 의학연구동(약국) 신축, International Village C동 리모델링, 반도체동(새늘동) 리모델링, 대강당 리모델링, 기계공학동 리모델링, Startup Village 리모델링, 서울캠퍼스 해정사와 8‧9호관 리모델링, 노천극장 리모델링, 화암기숙사 리모델링(예정), 에코 캠퍼스 구축(소나무 이식 등), 안전한 캠퍼스 구축(도로 및 보행자도로 개선 등) 등 신축공사와 노후건물 및 시설의 보수공사 등으로 빠르게 변화하였습니다. 인프라 확충사업 외에도, 문지캠퍼스에 IBS 사업단, 녹색교통대학원 등을 이전하여 기존 스페이스를 효율적으로 사용할 수 있는 방안에 대해 다양한 논의가 진행되고 있습니다.

국제화를 추구하고 다양성을 존중하는 문화는 앞으로 우리학교가 지속적으로 발전하는 원동력이 될 것입니다. 그동안 외국인 교원 10%, 외국인 학생 10%, 여성 교원 10%를 목표로 삼고 우수한 인재를 유치하기 위해 최선을 다한 결과 이제는 10:10:10 이니셔티브(Initiative)를 20:20:20 이니셔티브(Initiative)로 그 목표를 수정할 단계에 이르렀습니다. 나눔관 공동 Kitchen 환경개선, 교내 PODCAST를 통한 외국인 구성원들과의 소통, 할랄푸드 카페테리아(Hallal Food Cafeteria) 오픈, Bilingual 캠퍼스 구축사업, 해외 유수대학들과의 공동학위 프로그램 개설, 해외 인턴십 프로그램 확충, 젠더평등을 위한 제도개선, 여성휴게실 및 육아시설 개선 등 지금까지 우리가 기울였던 노력은 앞으로도 반드시 지속되어야 할 것입니다.

KAIST에 대한 국내외적 관심은 앞으로 더욱 커질 것으로 생각됩니다. 최근 4년간의 학부 지원자 경쟁률 추이가 가파르게 상승하고 있으며, 매우 우수한 학생들이 매년 입학하고 있습니다. 새내기는 물론 재학생들의 학교생활 만족도 또한 지속적으로 향상되면서 학생들의 학교에 대한 관심과 사랑으로 이어지고 있습니다. 최근 재학생, 동문, 학부모 등 우리학교와 직접적으로 관계된 분들의 기부가 급격히 늘어나는 새로운 기부문화가 형성되었고, 지난 4년간 기부건수는 2만 6천여건에 이르며 기부금 총액은 708억여원에 달합니다.국내외의 유수 기관에서 KAIST를 벤치마킹하기 위해 많은 분들이 찾아오고 있고, 몇몇 국가에서는 KAIST 분교를 자국에 설치해 달라는 요청을 한바 있습니다. 이러한 변화는 Happy Campus를 만들기 위한 우리 구성원들의 부단한 노력의 결과라고 생각합니다.

사랑하는 KAIST 가족 여러분,

2017년 신년사는 제가 KAIST 총장으로서 여러분께 드리는 마지막 신년사 입니다. 이사회에서 신임 총장 선임절차가 진행중이며, 2017년 2월 23일 이취임식을 끝으로 저는 여러분과 함께 했던 4년간의 KAIST 생활을 마치고 정들었던 교정을 떠납니다.

KAIST 총장으로서 제게 허락하는 시간까지 단 한 명의 구성원이라도 소외되지 않고 Happy Campus에서 꿈을 펼칠 수 있도록 최선을 다해 노력하겠습니다. 여러분과 함께 했던 지난 4년은 제게 큰 행복이자 영광이었습니다. KAIST를 세계 최고의 대학으로 성장시키고 해피 캠퍼스를 구축하기 위해 각자의 분야에서 헌신해 준 KAIST 전체 가족 여러분께 진심으로 감사드립니다.

여러분은 KAIST의 미래이자 대한민국을 이끌어가는 원동력입니다. 그동안 일구어낸 성과를 바탕으로 각자의 위치에서 인류와 국가의 발전에 공헌 할 수 있는 더욱 큰 꿈을 꾸고 그 꿈을 이루기 위해 최선을 다해주시길 바랍니다.

2017년은 우리 KAIST 가족 여러분의 모든 꿈이 실현되는 희망찬 한 해가 되기를 기원합니다. ‘제4차 산업혁명의 허브(hub)’이자 ‘Students-Centered, Faculty-Driven World’s Best Research University’를 향한 여러분의 도전을 응원합니다.

감사합니다.

2017년 1월 1일

KAIST 총장 강성모

2017.01.02 조회수 20984

2017년 총장 신년사

친애하는 KAIST 가족 여러분,

2017년 정유년(丁酉年) 새해가 밝았습니다. 새해 복 많이 받으시고, 댁내 건강과 행복이 가득하기를 기원합니다. 새해에도 여러분의 꿈이 이루어지고, 국민들로부터 큰 사랑과 믿음을 받고 있는 우리 KAIST가 그 성원에 보답할 수 있는 한해가 되기를 바랍니다.

2013년 총장으로 부임하며 Quantum Jump 전략을 수립하고, 전반기(2013~14)에는 ‘하나된 KAIST’를 만들어 구성원의 역량을 결집하고 후반기(2015~16)에는 ‘질적성장을 통해 혁신하는 KAIST’를 만들어 크게 도약하고자 노력했습니다. 지난 4년간 우리는 성장통을 지혜롭게 극복하며 눈부신 발전을 거듭했고, 명실상부한 ‘Students-Centered, Faculty-Driven, World’s Most Innovative Research University’로 발돋움 했습니다.

우리학교의 수월성을 달성하기 위한 ‘창의’와 ‘도전’은 국가발전의 원동력이 되어 왔습니다. 교육·연구·시스템의 지속적인 혁신, 창업문화의 확산, 대학의 사회적 책무를 다하고자 하는 노력들은 학교의 질적성장을 이끌어 왔습니다.